Design and Verification of Adaptive Cache Coherence Protocols ...

Design and Verification of Adaptive Cache Coherence Protocols ...

Design and Verification of Adaptive Cache Coherence Protocols ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

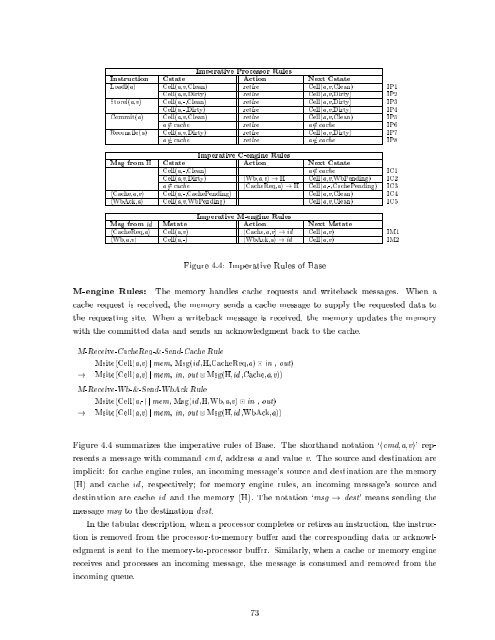

Imperative Processor Rules<br />

Instruction Cstate Action Next Cstate<br />

Loadl(a) Cell(a,v,Clean) retire Cell(a,v,Clean) IP1<br />

Cell(a,v,Dirty) retire Cell(a,v,Dirty) IP2<br />

Storel(a,v) Cell(a,-,Clean) retire Cell(a,v,Dirty) IP3<br />

Cell(a,-,Dirty) retire Cell(a,v,Dirty) IP4<br />

Commit(a) Cell(a,v,Clean) retire Cell(a,v,Clean) IP5<br />

a =2 cache retire a =2 cache IP6<br />

Reconcile(a) Cell(a,v,Dirty) retire Cell(a,v,Dirty) IP7<br />

a =2 cache retire a =2 cache IP8<br />

Imperative C-engine Rules<br />

Msg from H Cstate Action Next Cstate<br />

Cell(a,-,Clean) a =2 cache IC1<br />

Cell(a,v,Dirty) hWb,a,vi!H Cell(a,v,WbPending) IC2<br />

a =2 cache h<strong>Cache</strong>Req,ai !H Cell(a,-,<strong>Cache</strong>Pending) IC3<br />

h<strong>Cache</strong>,a,vi Cell(a,-,<strong>Cache</strong>Pending) Cell(a,v,Clean) IC4<br />

hWbAck,ai Cell(a,v,WbPending) Cell(a,v,Clean) IC5<br />

Imperative M-engine Rules<br />

Msg from id Mstate Action Next Mstate<br />

h<strong>Cache</strong>Req,ai Cell(a,v) h<strong>Cache</strong>,a,vi!id Cell(a,v) IM1<br />

hWb,a,vi Cell(a,-) hWbAck,ai !id Cell(a,v) IM2<br />

Figure 4.4: Imperative Rules <strong>of</strong> Base<br />

M-engine Rules: The memory h<strong>and</strong>les cache requests <strong>and</strong> writeback messages. When a<br />

cache request is received, the memory sends a cache message to supply the requested data to<br />

the requesting site. When a writeback message is received, the memory updates the memory<br />

with the committed data <strong>and</strong> sends an acknowledgment back tothecache.<br />

M-Receive-<strong>Cache</strong>Req-&-Send-<strong>Cache</strong> Rule<br />

Msite(Cell(a,v) j mem, Msg(id ,H,<strong>Cache</strong>Req,a) in , out)<br />

! Msite(Cell(a,v) j mem, in, out Msg(H,id ,<strong>Cache</strong>,a,v))<br />

M-Receive-Wb-&-Send-WbAck Rule<br />

Msite(Cell(a,-) j mem, Msg(id ,H,Wb,a,v) in , out)<br />

! Msite(Cell(a,v) j mem, in, out Msg(H,id ,WbAck,a))<br />

Figure 4.4 summarizes the imperative rules <strong>of</strong> Base. The shorth<strong>and</strong> notation `hcmd,a,vi' rep-<br />

resents a message with comm<strong>and</strong> cmd, address a <strong>and</strong> value v. The source <strong>and</strong> destination are<br />

implicit: for cache engine rules, an incoming message's source <strong>and</strong> destination are the memory<br />

(H) <strong>and</strong> cache id , respectively for memory engine rules, an incoming message's source <strong>and</strong><br />

destination are cache id <strong>and</strong> the memory (H). The notation `msg ! dest' means sending the<br />

message msg to the destination dest.<br />

In the tabular description, when a processor completes or retires an instruction, the instruc-<br />

tion is removed from the processor-to-memory bu er <strong>and</strong> the corresponding data or acknowl-<br />

edgment issent to the memory-to-processor bu er. Similarly, when a cache or memory engine<br />

receives <strong>and</strong> processes an incoming message, the message is consumed <strong>and</strong> removed from the<br />

incoming queue.<br />

73