Design and Verification of Adaptive Cache Coherence Protocols ...

Design and Verification of Adaptive Cache Coherence Protocols ...

Design and Verification of Adaptive Cache Coherence Protocols ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

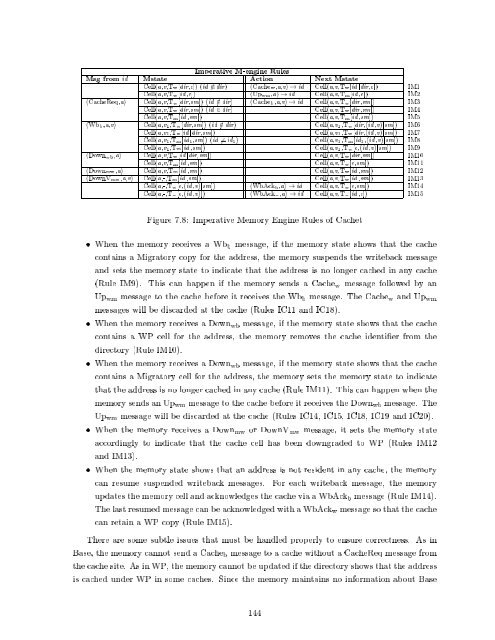

Imperative M-engine Rules<br />

Msg from id Mstate Action Next Mstate<br />

Cell(a,v,Tw[dir, ]) (id =2 dir) h<strong>Cache</strong>w,a,vi!id Cell(a,v,Tw[id jdir, ]) IM1<br />

Cell(a,v,Tw[id , ]) hUpwm,ai!id Cell(a,v,Tm[id , ]) IM2<br />

h<strong>Cache</strong>Req,ai Cell(a,v,Tw[dir,sm]) (id =2 dir) h<strong>Cache</strong>b,a,vi!id Cell(a,v,Tw[dir,sm]) IM3<br />

Cell(a,v,Tw[dir,sm]) (id 2 dir) Cell(a,v,Tw[dir,sm]) IM4<br />

Cell(a,v,Tm[id ,sm]) Cell(a,v,Tm[id ,sm]) IM5<br />

hWbb,a,vi Cell(a,v1,Tw[dir,sm]) (id =2 dir) Cell(a,v1,Tw[dir,(id ,v)jsm]) IM6<br />

Cell(a,v1,Tw[id jdir,sm]) Cell(a,v1,Tw[dir,(id ,v)jsm]) IM7<br />

Cell(a,v1,Tm[id1,sm]) (id 6= id1) Cell(a,v1,Tm[id1,(id ,v)jsm]) IM8<br />

Cell(a,v1,Tm[id ,sm]) Cell(a,v1,Tw[ ,(id ,v)jsm]) IM9<br />

hDownwb,ai Cell(a,v,Tw[id jdir,sm]) Cell(a,v,Tw[dir,sm]) IM10<br />

Cell(a,v,Tm[id ,sm]) Cell(a,v,Tw[ ,sm]) IM11<br />

hDownmw,ai Cell(a,v,Tm[id ,sm]) Cell(a,v,Tw[id ,sm]) IM12<br />

hDownVmw,a,vi Cell(a,-,Tm[id ,sm]) Cell(a,v,Tw[id ,sm]) IM13<br />

Cell(a,-,Tw[ ,(id ,v)jsm]) hWbAckb,ai!id Cell(a,v,Tw[ ,sm]) IM14<br />

Cell(a,-,Tw[ ,(id ,v)]) hWbAckw,ai!id Cell(a,v,Tw[id , ]) IM15<br />

Figure 7.8: Imperative Memory Engine Rules <strong>of</strong> <strong>Cache</strong>t<br />

When the memory receives a Wbb message, if the memory state shows that the cache<br />

contains a Migratory copy for the address, the memory suspends the writeback message<br />

<strong>and</strong> sets the memory state to indicate that the address is no longer cached in any cache<br />

(Rule IM9). This can happen if the memory sends a <strong>Cache</strong>w message followed by an<br />

Upwm message to the cache before it receives the Wbb message. The <strong>Cache</strong>w <strong>and</strong> Upwm<br />

messages will be discarded at the cache (Rules IC11 <strong>and</strong> IC18).<br />

When the memory receives a Downwb message, if the memory state shows that the cache<br />

contains a WP cell for the address, the memory removes the cache identi er from the<br />

directory (Rule IM10).<br />

When the memory receives a Downwb message, if the memory state shows that the cache<br />

contains a Migratory cell for the address, the memory sets the memory state to indicate<br />

that the address is no longer cached in any cache (Rule IM11). This can happen when the<br />

memory sends an Upwm message to the cache before it receives the Downwb message. The<br />

Upwm message will be discarded at the cache (Rules IC14, IC15, IC18, IC19 <strong>and</strong> IC20).<br />

When the memory receives a Downmw or DownVmw message, it sets the memory state<br />

accordingly to indicate that the cache cell has been downgraded to WP (Rules IM12<br />

<strong>and</strong> IM13).<br />

When the memory state shows that an address is not resident inanycache, the memory<br />

can resume suspended writeback messages. For each writeback message, the memory<br />

updates the memory cell <strong>and</strong> acknowledges the cache via a WbAckb message (Rule IM14).<br />

The last resumed message can be acknowledged with a WbAckw message so that the cache<br />

can retain a WP copy (Rule IM15).<br />

There are some subtle issues that must be h<strong>and</strong>led properly to ensure correctness. As in<br />

Base, the memory cannot send a <strong>Cache</strong>b message to a cache without a <strong>Cache</strong>Req message from<br />

the cache site. As in WP, the memory cannot be updated if the directory shows that the address<br />

is cached under WP in some caches. Since the memory maintains no information about Base<br />

144