Design and Verification of Adaptive Cache Coherence Protocols ...

Design and Verification of Adaptive Cache Coherence Protocols ...

Design and Verification of Adaptive Cache Coherence Protocols ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

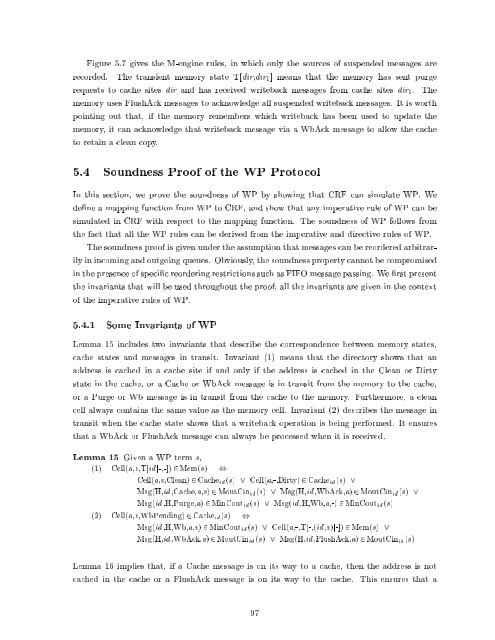

Figure 5.7 gives the M-engine rules, in which only the sources <strong>of</strong> suspended messages are<br />

recorded. The transient memory state T[dir,dir1] means that the memory has sent purge<br />

requests to cache sites dir <strong>and</strong> has received writeback messages from cache sites dir1. The<br />

memory uses FlushAck messages to acknowledge all suspended writeback messages. It is worth<br />

pointing out that, if the memory remembers which writeback has been used to update the<br />

memory, it can acknowledge that writeback message via a WbAck message to allow the cache<br />

to retain a clean copy.<br />

5.4 Soundness Pro<strong>of</strong> <strong>of</strong> the WP Protocol<br />

In this section, we prove the soundness <strong>of</strong> WP by showing that CRF can simulate WP. We<br />

de ne a mapping function from WP to CRF, <strong>and</strong> show thatany imperative rule <strong>of</strong> WP can be<br />

simulated in CRF with respect to the mapping function. The soundness <strong>of</strong> WP follows from<br />

the fact that all the WP rules can be derived from the imperative <strong>and</strong> directive rules <strong>of</strong> WP.<br />

The soundness pro<strong>of</strong> is given under the assumption that messages can be reordered arbitrar-<br />

ily in incoming <strong>and</strong> outgoing queues. Obviously, the soundness property cannot be compromised<br />

in the presence <strong>of</strong> speci c reordering restrictions such asFIFO message passing. We rst present<br />

the invariants that will be used throughout the pro<strong>of</strong> all the invariants are given in the context<br />

<strong>of</strong> the imperative rules <strong>of</strong> WP.<br />

5.4.1 Some Invariants <strong>of</strong> WP<br />

Lemma 15 includes two invariants that describe the correspondence between memory states,<br />

cache states <strong>and</strong> messages in transit. Invariant (1) means that the directory shows that an<br />

address is cached in a cache site if <strong>and</strong> only if the address is cached in the Clean or Dirty<br />

state in the cache, ora<strong>Cache</strong> or WbAck message is in transit from the memory to the cache,<br />

or a Purge or Wb message is in transit from the cache to the memory. Furthermore, a clean<br />

cell always contains the same value as the memory cell. Invariant (2) describes the message in<br />

transit when the cache state shows that a writeback operation is being performed. It ensures<br />

that a WbAck or FlushAck message can always be processed when it is received.<br />

Lemma 15 Given a WP term s,<br />

(1) Cell(a,v,T[id j-,-]) 2 Mem(s) ,<br />

Cell(a,v,Clean) 2 <strong>Cache</strong> id(s) _ Cell(a,-,Dirty) 2 <strong>Cache</strong> id(s) _<br />

Msg(H,id ,<strong>Cache</strong>,a,v) 2 MoutCin id (s) _ Msg(H,id ,WbAck,a) 2 MoutCin id (s) _<br />

Msg(id ,H,Purge,a) 2 MinCout id (s) _ Msg(id ,H,Wb,a,-) 2 MinCout id (s)<br />

(2) Cell(a,v,WbPending) 2 <strong>Cache</strong> id(s) ,<br />

Msg(id ,H,Wb,a,v) 2 MinCout id (s) _ Cell(a,-,T[-,(id ,v)j-]) 2 Mem(s) _<br />

Msg(H,id ,WbAck,a) 2 MoutCin id (s) _ Msg(H,id ,FlushAck,a) 2 MoutCin id (s)<br />

Lemma 16 implies that, if a <strong>Cache</strong> message is on its way to a cache, then the address is not<br />

cached in the cache or a FlushAck message is on its way to the cache. This ensures that a<br />

97