Design and Verification of Adaptive Cache Coherence Protocols ...

Design and Verification of Adaptive Cache Coherence Protocols ...

Design and Verification of Adaptive Cache Coherence Protocols ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

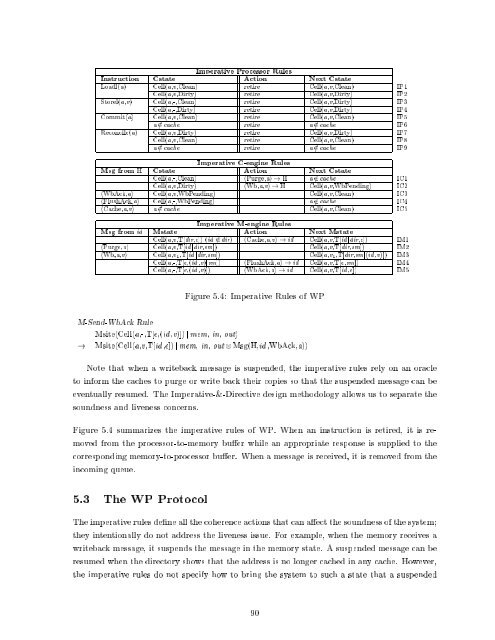

Imperative Processor Rules<br />

Instruction Cstate Action Next Cstate<br />

Loadl(a) Cell(a,v,Clean) retire Cell(a,v,Clean) IP1<br />

Cell(a,v,Dirty) retire Cell(a,v,Dirty) IP2<br />

Storel(a,v) Cell(a,-,Clean) retire Cell(a,v,Dirty) IP3<br />

Cell(a,-,Dirty) retire Cell(a,v,Dirty) IP4<br />

Commit(a) Cell(a,v,Clean) retire Cell(a,v,Clean) IP5<br />

a =2 cache retire a =2 cache IP6<br />

Reconcile(a) Cell(a,v,Dirty) retire Cell(a,v,Dirty) IP7<br />

Cell(a,v,Clean) retire Cell(a,v,Clean) IP8<br />

a =2 cache retire a =2 cache IP9<br />

Imperative C-engine Rules<br />

Msg from H Cstate Action Next Cstate<br />

Cell(a,-,Clean) hPurge,ai!H a =2 cache IC1<br />

Cell(a,v,Dirty) hWb,a,vi!H Cell(a,v,WbPending) IC2<br />

hWbAck,ai Cell(a,v,WbPending) Cell(a,v,Clean) IC3<br />

hFlushAck,ai Cell(a,-,WbPending) a =2 cache IC4<br />

h<strong>Cache</strong>,a,vi a =2 cache Cell(a,v,Clean) IC5<br />

Imperative M-engine Rules<br />

Msg from id Mstate Action Next Mstate<br />

Cell(a,v,T[dir, ]) (id =2 dir) h<strong>Cache</strong>,a,vi !id Cell(a,v,T[id jdir, ]) IM1<br />

hPurge,ai Cell(a,v,T[id jdir,sm]) Cell(a,v,T[dir,sm]) IM2<br />

hWb,a,vi Cell(a,v1,T[id jdir,sm]) Cell(a,v1,T[dir,smj(id ,v)]) IM3<br />

Cell(a,-,T[ ,(id ,v)jsm]) hFlushAck,ai!id Cell(a,v,T[ ,sm]) IM4<br />

Cell(a,-,T[ ,(id ,v)]) hWbAck,ai !id Cell(a,v,T[id , ]) IM5<br />

Figure 5.4: Imperative Rules <strong>of</strong> WP<br />

M-Send-WbAck Rule<br />

Msite(Cell(a,-,T[ ,(id ,v)]) j mem, in, out)<br />

! Msite(Cell(a,v,T[id , ]) j mem, in, out Msg(H,id ,WbAck,a))<br />

Note that when a writeback message is suspended, the imperative rules rely on an oracle<br />

to inform the caches to purge or write back their copies so that the suspended message can be<br />

eventually resumed. The Imperative-&-Directive design methodology allows us to separate the<br />

soundness <strong>and</strong> liveness concerns.<br />

Figure 5.4 summarizes the imperative rules <strong>of</strong> WP. When an instruction is retired, it is re-<br />

moved from the processor-to-memory bu er while an appropriate response is supplied to the<br />

corresponding memory-to-processor bu er. When a message is received,itisremoved from the<br />

incoming queue.<br />

5.3 The WP Protocol<br />

The imperative rules de ne all the coherence actions that can a ect the soundness <strong>of</strong> the system<br />

they intentionally do not address the liveness issue. For example, when the memory receives a<br />

writeback message, it suspends the message in the memory state. A suspended message can be<br />

resumed when the directory shows that the address is no longer cached in any cache. However,<br />

the imperative rules do not specify how to bring the system to such a state that a suspended<br />

90