Design and Verification of Adaptive Cache Coherence Protocols ...

Design and Verification of Adaptive Cache Coherence Protocols ...

Design and Verification of Adaptive Cache Coherence Protocols ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

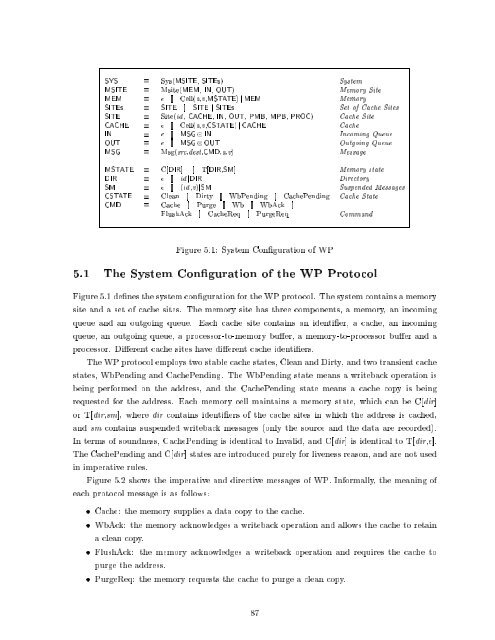

SYS Sys(MSITE, SITEs) System<br />

MSITE Msite(MEM, IN, OUT) Memory Site<br />

MEM [] Cell(a,v,MSTATE) j MEM Memory<br />

SITEs SITE [] SITE j SITEs Set <strong>of</strong> <strong>Cache</strong> Sites<br />

SITE Site(id , CACHE, IN, OUT, PMB, MPB, PROC) <strong>Cache</strong> Site<br />

CACHE [] Cell(a,v,CSTATE) j CACHE <strong>Cache</strong><br />

IN [] MSG IN Incoming Queue<br />

OUT [] MSG OUT Outgoing Queue<br />

MSG Msg(src,dest,CMD,a,v) Message<br />

MSTATE C[DIR] [] T[DIR,SM] Memory state<br />

DIR [] id jDIR Directory<br />

SM [] (id ,v)jSM Suspended Messages<br />

CSTATE Clean [] Dirty [] WbPending [] <strong>Cache</strong>Pending <strong>Cache</strong> State<br />

CMD <strong>Cache</strong> [] Purge [] Wb [] WbAck []<br />

FlushAck [] <strong>Cache</strong>Req [] PurgeReq Comm<strong>and</strong><br />

Figure 5.1: System Con guration <strong>of</strong> WP<br />

5.1 The System Con guration <strong>of</strong> the WP Protocol<br />

Figure 5.1 de nes the system con guration for the WP protocol. The system contains a memory<br />

site <strong>and</strong> a set <strong>of</strong> cache sites. The memory site has three components, a memory, an incoming<br />

queue <strong>and</strong> an outgoing queue. Each cache site contains an identi er, a cache, an incoming<br />

queue, an outgoing queue, a processor-to-memory bu er, a memory-to-processor bu er <strong>and</strong> a<br />

processor. Di erent cache sites have di erent cache identi ers.<br />

The WP protocol employs two stable cache states, Clean <strong>and</strong> Dirty, <strong>and</strong> two transient cache<br />

states, WbPending <strong>and</strong> <strong>Cache</strong>Pending. The WbPending state means a writeback operation is<br />

being performed on the address, <strong>and</strong> the <strong>Cache</strong>Pending state means a cache copy is being<br />

requested for the address. Each memory cell maintains a memory state, which can be C[dir]<br />

or T[dir,sm], where dir contains identi ers <strong>of</strong> the cache sites in which the address is cached,<br />

<strong>and</strong> sm contains suspended writeback messages (only the source <strong>and</strong> the data are recorded).<br />

In terms <strong>of</strong> soundness, <strong>Cache</strong>Pending is identical to Invalid, <strong>and</strong> C[dir] is identical to T[dir, ].<br />

The <strong>Cache</strong>Pending <strong>and</strong> C[dir] states are introduced purely for liveness reason, <strong>and</strong> are not used<br />

in imperative rules.<br />

Figure 5.2 shows the imperative <strong>and</strong> directive messages <strong>of</strong> WP. Informally, the meaning <strong>of</strong><br />

each protocol message is as follows:<br />

<strong>Cache</strong>: the memory supplies a data copy tothecache.<br />

WbAck: the memory acknowledges a writeback operation <strong>and</strong> allows the cache to retain<br />

a clean copy.<br />

FlushAck: the memory acknowledges a writeback operation <strong>and</strong> requires the cache to<br />

purge the address.<br />

PurgeReq: the memory requests the cache to purge a clean copy.<br />

87