Design and Verification of Adaptive Cache Coherence Protocols ...

Design and Verification of Adaptive Cache Coherence Protocols ...

Design and Verification of Adaptive Cache Coherence Protocols ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

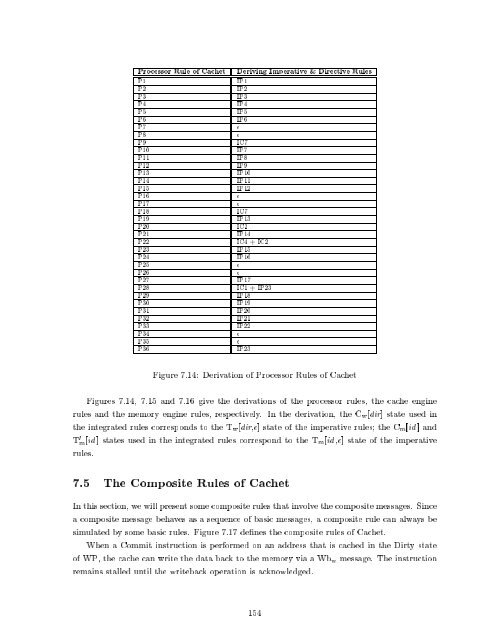

Processor Rule <strong>of</strong> <strong>Cache</strong>t Deriving Imperative & Directive Rules<br />

P1 IP1<br />

P2 IP2<br />

P3 IP3<br />

P4 IP4<br />

P5 IP5<br />

P6 IP6<br />

P7<br />

P8<br />

P9 IC7<br />

P10 IP7<br />

P11 IP8<br />

P12 IP9<br />

P13 IP10<br />

P14 IP11<br />

P15 IP12<br />

P16<br />

P17<br />

P18 IC7<br />

P19 IP13<br />

P20 IC2<br />

P21 IP14<br />

P22 IC4 + IC2<br />

P23 IP15<br />

P24 IP16<br />

P25<br />

P26<br />

P27 IP17<br />

P28 IC1+IP23<br />

P29 IP18<br />

P30 IP19<br />

P31 IP20<br />

P32 IP21<br />

P33 IP22<br />

P34<br />

P35<br />

P36 IP23<br />

Figure 7.14: Derivation <strong>of</strong> Processor Rules <strong>of</strong> <strong>Cache</strong>t<br />

Figures 7.14, 7.15 <strong>and</strong> 7.16 give the derivations <strong>of</strong> the processor rules, the cache engine<br />

rules <strong>and</strong> the memory engine rules, respectively. In the derivation, the Cw[dir] state used in<br />

the integrated rules corresponds to the Tw[dir, ] state <strong>of</strong> the imperative rules the Cm[id ] <strong>and</strong><br />

T 0 m [id ] states used in the integrated rules correspond to the Tm[id , ] state <strong>of</strong> the imperative<br />

rules.<br />

7.5 The Composite Rules <strong>of</strong> <strong>Cache</strong>t<br />

In this section, we will present some composite rules that involve the composite messages. Since<br />

a composite message behaves as a sequence <strong>of</strong> basic messages, a composite rule can always be<br />

simulated by some basic rules. Figure 7.17 de nes the composite rules <strong>of</strong> <strong>Cache</strong>t.<br />

When a Commit instruction is performed on an address that is cached in the Dirty state<br />

<strong>of</strong> WP, the cache can write the data back to the memory via a Wbw message. The instruction<br />

remains stalled until the writeback operation is acknowledged.<br />

154