Design and Verification of Adaptive Cache Coherence Protocols ...

Design and Verification of Adaptive Cache Coherence Protocols ...

Design and Verification of Adaptive Cache Coherence Protocols ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

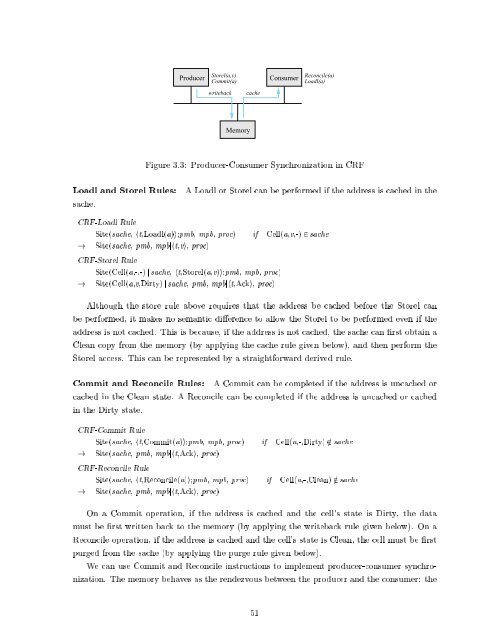

Producer<br />

Storel(a,v)<br />

Commit(a)<br />

Consumer<br />

writeback<br />

Memory<br />

cache<br />

Reconcile(a)<br />

Loadl(a)<br />

Figure 3.3: Producer-Consumer Synchronization in CRF<br />

Loadl <strong>and</strong> Storel Rules: A Loadl or Storel can be performed if the address is cached in the<br />

sache.<br />

CRF-Loadl Rule<br />

Site(sache, ht,Loadl(a)ipmb, mpb, proc) if Cell(a,v,-) 2 sache<br />

! Site(sache, pmb, mpbjht,vi, proc)<br />

CRF-Storel Rule<br />

Site(Cell(a,-,-) j sache, ht,Storel(a,v)ipmb, mpb, proc)<br />

! Site(Cell(a,v,Dirty) j sache, pmb, mpbjht,Acki, proc)<br />

Although the store rule above requires that the address be cached before the Storel can<br />

be performed, it makes no semantic di erence to allow the Storel to be performed even if the<br />

address is not cached. This is because, if the address is not cached, the sache can rst obtain a<br />

Clean copy from the memory (by applying the cache rule given below), <strong>and</strong> then perform the<br />

Storel access. This can be represented by a straightforward derived rule.<br />

Commit <strong>and</strong> Reconcile Rules: A Commit can be completed if the address is uncached or<br />

cached in the Clean state. A Reconcile can be completed if the address is uncached or cached<br />

in the Dirty state.<br />

CRF-Commit Rule<br />

Site(sache, ht,Commit(a)ipmb, mpb, proc) if Cell(a,-,Dirty) =2 sache<br />

! Site(sache, pmb, mpbjht,Acki, proc)<br />

CRF-Reconcile Rule<br />

Site(sache, ht,Reconcile(a)ipmb, mpb, proc) if Cell(a,-,Clean) =2 sache<br />

! Site(sache, pmb, mpbjht,Acki, proc)<br />

On a Commit operation, if the address is cached <strong>and</strong> the cell's state is Dirty, the data<br />

must be rst written back to the memory (by applying the writeback rulegiven below). On a<br />

Reconcile operation, if the address is cached <strong>and</strong> the cell's state is Clean, the cell must be rst<br />

purged from the sache (by applying the purge rule given below).<br />

We can use Commit <strong>and</strong> Reconcile instructions to implement producer-consumer synchro-<br />

nization. The memory behaves as the rendezvous between the producer <strong>and</strong> the consumer: the<br />

51