Design and Verification of Adaptive Cache Coherence Protocols ...

Design and Verification of Adaptive Cache Coherence Protocols ...

Design and Verification of Adaptive Cache Coherence Protocols ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Invalid<br />

Commit/Reconcile<br />

Receive <strong>Cache</strong>w<br />

Receive <strong>Cache</strong>w<br />

Send Downmw<br />

Loadl/Commit/Reconcile<br />

Loadl/Commit/Reconcile Loadl/Storel/Commit/Reconcile<br />

Clean Dirty<br />

m m<br />

Receive Up wm<br />

Send Downmb<br />

Storel<br />

Send DownVmw<br />

Clean Dirty<br />

w w<br />

Receive WbAckw<br />

Send Downmb<br />

Send <strong>Cache</strong>Req<br />

Receive <strong>Cache</strong>b<br />

Receive WbAckb<br />

Send Wb b<br />

<strong>Cache</strong>-<br />

Pending Cleanb Wb-<br />

Pending<br />

Dirtyb<br />

Purge<br />

Receive Up wm<br />

Storel Loadl/Storel/Reconcile<br />

Receive <strong>Cache</strong>w<br />

Loadl/Commit Storel<br />

Loadl/Storel/Reconcile<br />

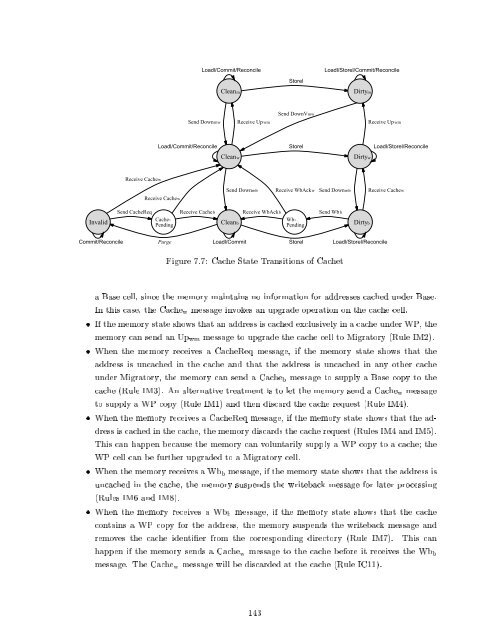

Figure 7.7: <strong>Cache</strong> State Transitions <strong>of</strong> <strong>Cache</strong>t<br />

a Base cell, since the memory maintains no information for addresses cached under Base.<br />

In this case, the <strong>Cache</strong>w message invokes an upgrade operation on the cache cell.<br />

If the memory state shows that an address is cached exclusively in a cache under WP, the<br />

memory can send an Upwm message to upgrade the cache cell to Migratory (Rule IM2).<br />

When the memory receives a <strong>Cache</strong>Req message, if the memory state shows that the<br />

address is uncached in the cache <strong>and</strong> that the address is uncached in any other cache<br />

under Migratory, the memory can send a <strong>Cache</strong>b message to supply a Base copy to the<br />

cache (Rule IM3). An alternative treatment is to let the memory send a <strong>Cache</strong>w message<br />

to supply a WP copy (Rule IM1) <strong>and</strong> then discard the cache request (Rule IM4).<br />

When the memory receivesa<strong>Cache</strong>Req message, if the memory state shows that the ad-<br />

dress is cached in the cache, the memory discards the cache request (Rules IM4 <strong>and</strong> IM5).<br />

This can happen because the memory can voluntarily supply a WP copy toacache the<br />

WP cell can be further upgraded to a Migratory cell.<br />

When the memory receives a Wbb message, if the memory state shows that the address is<br />

uncached in the cache, the memory suspends the writeback message for later processing<br />

(Rules IM6 <strong>and</strong> IM8).<br />

When the memory receives a Wbb message, if the memory state shows that the cache<br />

contains a WP copy for the address, the memory suspends the writeback message <strong>and</strong><br />

removes the cache identi er from the corresponding directory (Rule IM7). This can<br />

happen if the memory sends a <strong>Cache</strong>w message to the cache before it receives the Wbb<br />

message. The <strong>Cache</strong>w message will be discarded at the cache (Rule IC11).<br />

143