Design and Verification of Adaptive Cache Coherence Protocols ...

Design and Verification of Adaptive Cache Coherence Protocols ...

Design and Verification of Adaptive Cache Coherence Protocols ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

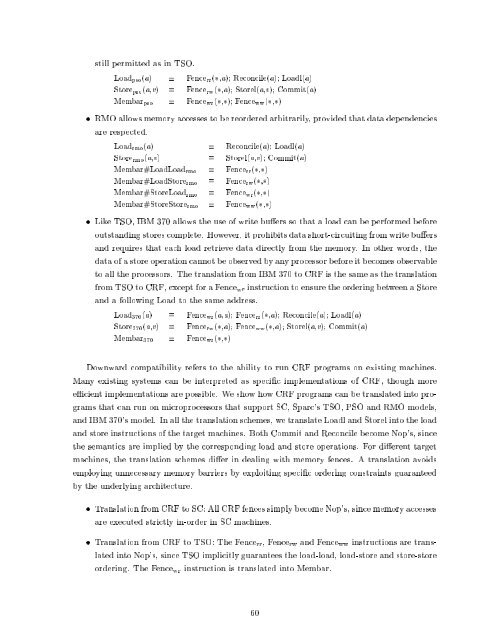

still permitted as in TSO.<br />

Loadpso(a) Fencerr( ,a) Reconcile(a) Loadl(a)<br />

Storepso(a,v) Fencerw( ,a) Storel(a,v) Commit(a)<br />

Membarpso Fencewr( , ) Fenceww( , )<br />

RMO allows memory accesses to be reordered arbitrarily,provided that data dependencies<br />

are respected.<br />

Loadrmo(a) Reconcile(a) Loadl(a)<br />

Storermo(a,v) Storel(a,v) Commit(a)<br />

Membar#LoadLoadrmo Fencerr( , )<br />

Membar#LoadStorermo Fencerw( , )<br />

Membar#StoreLoadrmo Fencewr( , )<br />

Membar#StoreStorermo Fenceww( , )<br />

Like TSO, IBM 370 allows the use <strong>of</strong> write bu ers so that a load can be performed before<br />

outst<strong>and</strong>ing stores complete. However, it prohibits data short-circuiting from write bu ers<br />

<strong>and</strong> requires that each load retrieve data directly from the memory. In other words, the<br />

data <strong>of</strong> a store operation cannot be observed byany processor before it becomes observable<br />

to all the processors. The translation from IBM 370 to CRF is the same as the translation<br />

from TSO to CRF, except for a Fencewr instruction to ensure the ordering between a Store<br />

<strong>and</strong> a following Load to the same address.<br />

Load370(a) Fencewr(a,a) Fencerr( ,a) Reconcile(a) Loadl(a)<br />

Store370(a,v) Fencerw( ,a) Fenceww( ,a) Storel(a,v) Commit(a)<br />

Membar370 Fencewr( , )<br />

Downward compatibility refers to the ability to run CRF programs on existing machines.<br />

Many existing systems can be interpreted as speci c implementations <strong>of</strong> CRF, though more<br />

e cient implementations are possible. We showhow CRF programs can be translated into pro-<br />

grams that can run on microprocessors that support SC, Sparc's TSO, PSO <strong>and</strong> RMO models,<br />

<strong>and</strong> IBM 370's model. In all the translation schemes, we translate Loadl <strong>and</strong> Storel into the load<br />

<strong>and</strong> store instructions <strong>of</strong> the target machines. Both Commit <strong>and</strong> Reconcile become Nop's, since<br />

the semantics are implied by the corresponding load <strong>and</strong> store operations. For di erent target<br />

machines, the translation schemes di er in dealing with memory fences. A translation avoids<br />

employing unnecessary memory barriers by exploiting speci c ordering constraints guaranteed<br />

by the underlying architecture.<br />

Translation from CRF to SC: All CRF fences simply become Nop's, since memory accesses<br />

are executed strictly in-order in SC machines.<br />

Translation from CRF to TSO: The Fencerr, Fencerw <strong>and</strong> Fenceww instructions are trans-<br />

lated into Nop's, since TSO implicitly guarantees the load-load, load-store <strong>and</strong> store-store<br />

ordering. The Fencewr instruction is translated into Membar.<br />

60