Hardware-Entwurf mit VHDL

Hardware-Entwurf mit VHDL

Hardware-Entwurf mit VHDL

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

<strong>Hardware</strong>-<strong>Entwurf</strong> <strong>mit</strong> <strong>VHDL</strong><br />

Prof. Dr.-Ing. Stefan Wolter Elektrotechnik und Informatik<br />

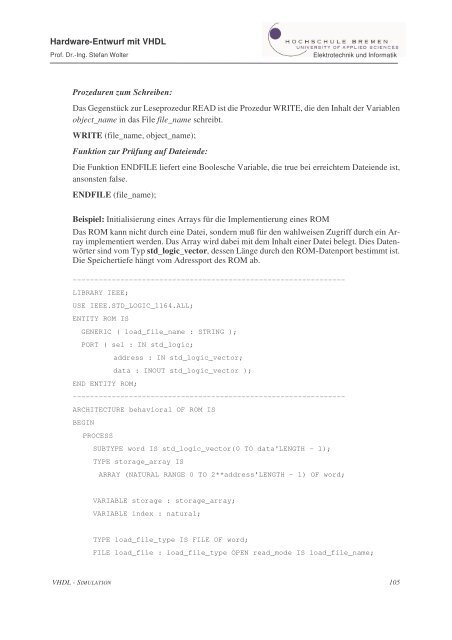

Prozeduren zum Schreiben:<br />

Das Gegenstück zur Leseprozedur READ ist die Prozedur WRITE, die den Inhalt der Variablen<br />

object_name in das File file_name schreibt.<br />

WRITE (file_name, object_name);<br />

Funktion zur Prüfung auf Dateiende:<br />

Die Funktion ENDFILE liefert eine Boolesche Variable, die true bei erreichtem Dateiende ist,<br />

ansonsten false.<br />

ENDFILE (file_name);<br />

Beispiel: Initialisierung eines Arrays für die Implementierung eines ROM<br />

Das ROM kann nicht durch eine Datei, sondern muß für den wahlweisen Zugriff durch ein Array<br />

implementiert werden. Das Array wird dabei <strong>mit</strong> dem Inhalt einer Datei belegt. Dies Datenwörter<br />

sind vom Typ std_logic_vector, dessen Länge durch den ROM-Datenport bestimmt ist.<br />

Die Speichertiefe hängt vom Adressport des ROM ab.<br />

---------------------------------------------------------------<br />

LIBRARY IEEE;<br />

USE IEEE.STD_LOGIC_1164.ALL;<br />

ENTITY ROM IS<br />

GENERIC ( load_file_name : STRING );<br />

PORT ( sel : IN std_logic;<br />

END ENTITY ROM;<br />

address : IN std_logic_vector;<br />

data : INOUT std_logic_vector );<br />

---------------------------------------------------------------<br />

ARCHITECTURE behavioral OF ROM IS<br />

BEGIN<br />

PROCESS<br />

SUBTYPE word IS std_logic_vector(0 TO data'LENGTH - 1);<br />

TYPE storage_array IS<br />

ARRAY (NATURAL RANGE 0 TO 2**address'LENGTH - 1) OF word;<br />

VARIABLE storage : storage_array;<br />

VARIABLE index : natural;<br />

TYPE load_file_type IS FILE OF word;<br />

FILE load_file : load_file_type OPEN read_mode IS load_file_name;<br />

<strong>VHDL</strong> - SIMULATION 105