Hardware-Entwurf mit VHDL

Hardware-Entwurf mit VHDL

Hardware-Entwurf mit VHDL

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

<strong>Hardware</strong>-<strong>Entwurf</strong> <strong>mit</strong> <strong>VHDL</strong><br />

Prof. Dr.-Ing. Stefan Wolter Elektrotechnik und Informatik<br />

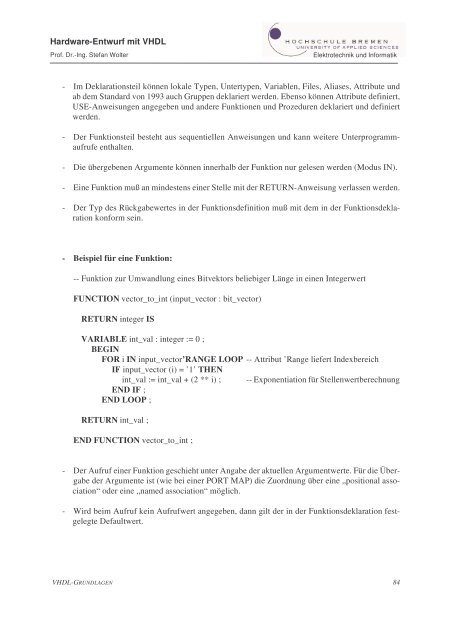

- Im Deklarationsteil können lokale Typen, Untertypen, Variablen, Files, Aliases, Attribute und<br />

ab dem Standard von 1993 auch Gruppen deklariert werden. Ebenso können Attribute definiert,<br />

USE-Anweisungen angegeben und andere Funktionen und Prozeduren deklariert und definiert<br />

werden.<br />

- Der Funktionsteil besteht aus sequentiellen Anweisungen und kann weitere Unterprogrammaufrufe<br />

enthalten.<br />

- Die übergebenen Argumente können innerhalb der Funktion nur gelesen werden (Modus IN).<br />

- Eine Funktion muß an mindestens einer Stelle <strong>mit</strong> der RETURN-Anweisung verlassen werden.<br />

- Der Typ des Rückgabewertes in der Funktionsdefinition muß <strong>mit</strong> dem in der Funktionsdeklaration<br />

konform sein.<br />

- Beispiel für eine Funktion:<br />

-- Funktion zur Umwandlung eines Bitvektors beliebiger Länge in einen Integerwert<br />

FUNCTION vector_to_int (input_vector : bit_vector)<br />

RETURN integer IS<br />

VARIABLE int_val : integer := 0 ;<br />

BEGIN<br />

FOR i IN input_vector’RANGE LOOP -- Attribut ’Range liefert Indexbereich<br />

IF input_vector (i) = ’1’ THEN<br />

int_val := int_val + (2 ** i) ; -- Exponentiation für Stellenwertberechnung<br />

END IF ;<br />

END LOOP ;<br />

RETURN int_val ;<br />

END FUNCTION vector_to_int ;<br />

- Der Aufruf einer Funktion geschieht unter Angabe der aktuellen Argumentwerte. Für die Übergabe<br />

der Argumente ist (wie bei einer PORT MAP) die Zuordnung über eine „positional association“<br />

oder eine „named association“ möglich.<br />

- Wird beim Aufruf kein Aufrufwert angegeben, dann gilt der in der Funktionsdeklaration festgelegte<br />

Defaultwert.<br />

<strong>VHDL</strong>-GRUNDLAGEN 84