Hardware-Entwurf mit VHDL

Hardware-Entwurf mit VHDL

Hardware-Entwurf mit VHDL

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

<strong>Hardware</strong>-<strong>Entwurf</strong> <strong>mit</strong> <strong>VHDL</strong><br />

Prof. Dr.-Ing. Stefan Wolter Elektrotechnik und Informatik<br />

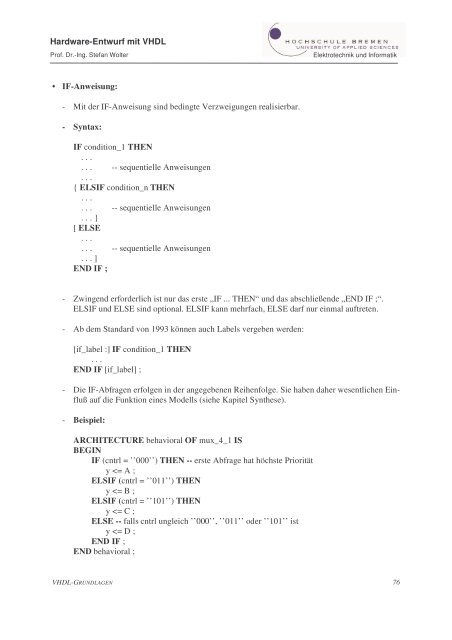

• IF-Anweisung:<br />

- Mit der IF-Anweisung sind bedingte Verzweigungen realisierbar.<br />

- Syntax:<br />

IF condition_1 THEN<br />

. . .<br />

. . . -- sequentielle Anweisungen<br />

. . .<br />

{ ELSIF condition_n THEN<br />

. . .<br />

. . . -- sequentielle Anweisungen<br />

. . . }<br />

[ ELSE<br />

. . .<br />

. . . -- sequentielle Anweisungen<br />

. . . ]<br />

END IF ;<br />

- Zwingend erforderlich ist nur das erste „IF ... THEN“ und das abschließende „END IF ;“.<br />

ELSIF und ELSE sind optional. ELSIF kann mehrfach, ELSE darf nur einmal auftreten.<br />

- Ab dem Standard von 1993 können auch Labels vergeben werden:<br />

[if_label :] IF condition_1 THEN<br />

. . .<br />

END IF [if_label] ;<br />

- Die IF-Abfragen erfolgen in der angegebenen Reihenfolge. Sie haben daher wesentlichen Einfluß<br />

auf die Funktion eines Modells (siehe Kapitel Synthese).<br />

- Beispiel:<br />

ARCHITECTURE behavioral OF mux_4_1 IS<br />

BEGIN<br />

IF (cntrl = ’’000’’) THEN -- erste Abfrage hat höchste Priorität<br />

y