Hardware-Entwurf mit VHDL

Hardware-Entwurf mit VHDL

Hardware-Entwurf mit VHDL

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

<strong>Hardware</strong>-<strong>Entwurf</strong> <strong>mit</strong> <strong>VHDL</strong><br />

Prof. Dr.-Ing. Stefan Wolter Elektrotechnik und Informatik<br />

6.2 Einflüsse auf das Syntheseergebnis<br />

Synthesewerkzeuge bilden Synthesemodelle auf Strukturen <strong>mit</strong> verfügbaren Komponenten ab. Dies<br />

erfolgt abhängig vom Modell, von der Bibliothek/Zielhardware und der Steuerung des Werkzeugs.<br />

Für Schaltungen gibt es immer mehrere Modellierungsvarianten. Durch geschickte Verwendung von<br />

Sprachelementen kann bereits bei der Modellierung eine Entscheidung über eine mehr oder weniger<br />

geeignete Schaltung getroffen werden.<br />

Neben dem Modellierungsstil haben die verfügbaren Komponenten und die Steuerung des Syntheseprogramms<br />

erheblichen Einfluß auf das Ergebnis. Der Benutzer gibt durch das Synthesemodell vor,<br />

welche Funktion er realisiert haben möchte. Durch die Angabe von Synthesezielen und Randbedingungen<br />

(Constraints) kann er dem Syntheseprogramm vorgeben, welche Ziele erfüllt werden sollen.<br />

<strong>VHDL</strong>-Modell<br />

(Modellierungsstil)<br />

Synthesewerkzeug<br />

Bibliothek/ Vorgaben/Steuerung<br />

Zielhardware des Synthesewerkzeugs<br />

Abbildung 6.1: Einflüsse auf das Syntheseergebnis<br />

Syntheseergebnis<br />

Grundlegende Syntheseziele sind neben einer funktionierenden Schaltung ein möglichst geringer Flächenverbrauch<br />

und eine möglichst hohe Taktfrequenz. Die Constraints können über Menüs oder Befehlsskripte<br />

vorgegeben werden. Nach dem Syntheselauf liefern die Synthesewerkzeuge die Information,<br />

ob und inwieweit die Vorgaben eingehalten wurden.<br />

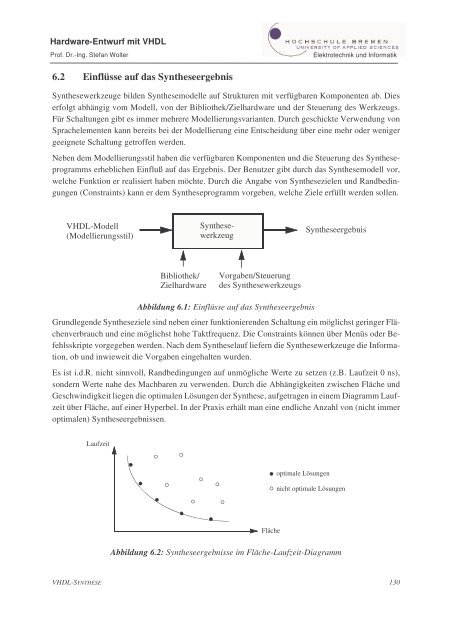

Es ist i.d.R. nicht sinnvoll, Randbedingungen auf unmögliche Werte zu setzen (z.B. Laufzeit 0 ns),<br />

sondern Werte nahe des Machbaren zu verwenden. Durch die Abhängigkeiten zwischen Fläche und<br />

Geschwindigkeit liegen die optimalen Lösungen der Synthese, aufgetragen in einem Diagramm Laufzeit<br />

über Fläche, auf einer Hyperbel. In der Praxis erhält man eine endliche Anzahl von (nicht immer<br />

optimalen) Syntheseergebnissen.<br />

Laufzeit<br />

Fläche<br />

optimale Lösungen<br />

nicht optimale Lösungen<br />

Abbildung 6.2: Syntheseergebnisse im Fläche-Laufzeit-Diagramm<br />

<strong>VHDL</strong>-SYNTHESE 130