Hardware-Entwurf mit VHDL

Hardware-Entwurf mit VHDL

Hardware-Entwurf mit VHDL

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

<strong>Hardware</strong>-<strong>Entwurf</strong> <strong>mit</strong> <strong>VHDL</strong><br />

Prof. Dr.-Ing. Stefan Wolter Elektrotechnik und Informatik<br />

3.2 Validierung <strong>mit</strong> einer Testbench<br />

Mit einer Testumgebung („Testbench“) wird die korrekte Funktionsweise einer zu entwerfenden<br />

Schaltung (sog. Device Under Test) unter Verwendung von Stimulidaten geprüft (validiert). Im besten<br />

Fall stellen die Testbenches nicht nur die Stimulidaten zur Verfügung, sondern sie prüfen auch<br />

die Ausgangssignale (sog. self-checking testbenches).<br />

Testbenches können aus einem oder aus mehreren <strong>VHDL</strong>-Modellen aufgebaut werden.<br />

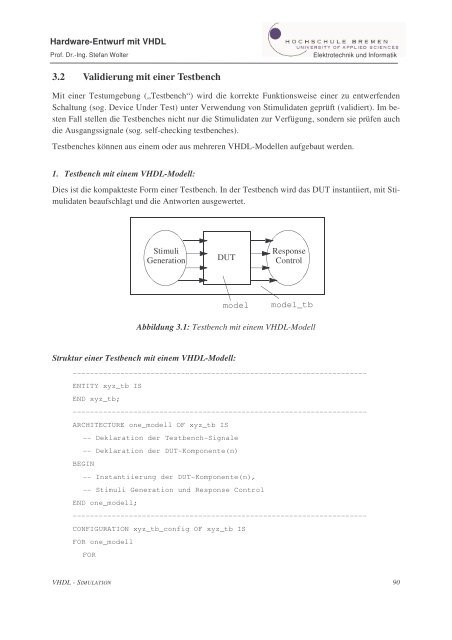

1. Testbench <strong>mit</strong> einem <strong>VHDL</strong>-Modell:<br />

Dies ist die kompakteste Form einer Testbench. In der Testbench wird das DUT instantiiert, <strong>mit</strong> Stimulidaten<br />

beaufschlagt und die Antworten ausgewertet.<br />

Abbildung 3.1: Testbench <strong>mit</strong> einem <strong>VHDL</strong>-Modell<br />

Struktur einer Testbench <strong>mit</strong> einem <strong>VHDL</strong>-Modell:<br />

--------------------------------------------------------------------<br />

ENTITY xyz_tb IS<br />

END xyz_tb;<br />

--------------------------------------------------------------------<br />

ARCHITECTURE one_modell OF xyz_tb IS<br />

-- Deklaration der Testbench-Signale<br />

-- Deklaration der DUT-Komponente(n)<br />

BEGIN<br />

-- Instantiierung der DUT-Komponente(n),<br />

-- Stimuli Generation und Response Control<br />

END one_modell;<br />

--------------------------------------------------------------------<br />

CONFIGURATION xyz_tb_config OF xyz_tb IS<br />

FOR one_modell<br />

FOR<br />

Stimuli<br />

Generation<br />

DUT<br />

Response<br />

Control<br />

model model_tb<br />

<strong>VHDL</strong> - SIMULATION 90