Hardware-Entwurf mit VHDL

Hardware-Entwurf mit VHDL

Hardware-Entwurf mit VHDL

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

<strong>Hardware</strong>-<strong>Entwurf</strong> <strong>mit</strong> <strong>VHDL</strong><br />

Prof. Dr.-Ing. Stefan Wolter Elektrotechnik und Informatik<br />

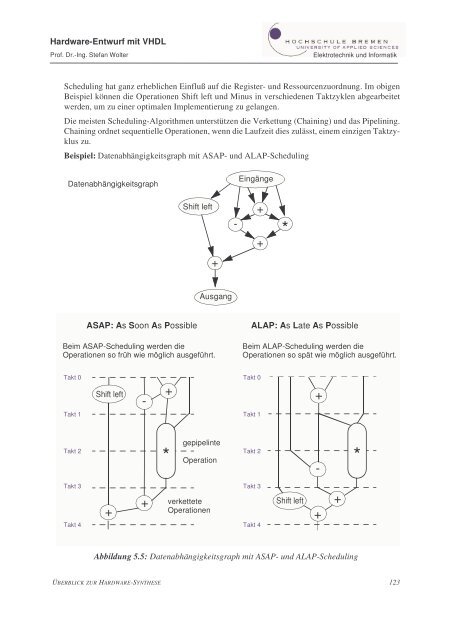

Scheduling hat ganz erheblichen Einfluß auf die Register- und Ressourcenzuordnung. Im obigen<br />

Beispiel können die Operationen Shift left und Minus in verschiedenen Taktzyklen abgearbeitet<br />

werden, um zu einer optimalen Implementierung zu gelangen.<br />

Die meisten Scheduling-Algorithmen unterstützen die Verkettung (Chaining) und das Pipelining.<br />

Chaining ordnet sequentielle Operationen, wenn die Laufzeit dies zulässt, einem einzigen Taktzyklus<br />

zu.<br />

Beispiel: Datenabhängigkeitsgraph <strong>mit</strong> ASAP- und ALAP-Scheduling<br />

Datenabhängigkeitsgraph<br />

Takt 0<br />

Takt 1<br />

Takt 2<br />

Takt 3<br />

Takt 4<br />

Shift left<br />

+<br />

-<br />

+<br />

+<br />

*<br />

Eingänge<br />

Shift left +<br />

+<br />

Ausgang<br />

- *<br />

+<br />

ASAP: As Soon As Possible ALAP: As Late As Possible<br />

Beim ASAP-Scheduling werden die<br />

Operationen so früh wie möglich ausgeführt.<br />

gepipelinte<br />

Operation<br />

verkettete<br />

Operationen<br />

Beim ALAP-Scheduling werden die<br />

Operationen so spät wie möglich ausgeführt.<br />

Takt 0<br />

Takt 1<br />

Takt 2<br />

Takt 3<br />

Takt 4<br />

Shift left<br />

Abbildung 5.5: Datenabhängigkeitsgraph <strong>mit</strong> ASAP- und ALAP-Scheduling<br />

ÜBERBLICK ZUR HARDWARE-SYNTHESE 123<br />

+<br />

-<br />

+<br />

+<br />

*