Hardware-Entwurf mit VHDL

Hardware-Entwurf mit VHDL

Hardware-Entwurf mit VHDL

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

<strong>Hardware</strong>-<strong>Entwurf</strong> <strong>mit</strong> <strong>VHDL</strong><br />

Prof. Dr.-Ing. Stefan Wolter Elektrotechnik und Informatik<br />

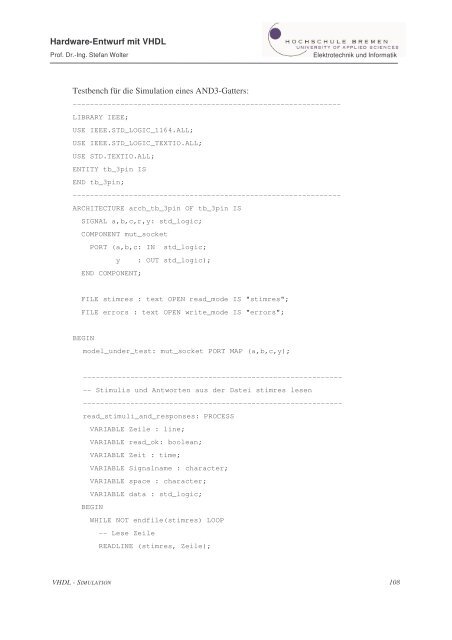

Testbench für die Simulation eines AND3-Gatters:<br />

--------------------------------------------------------------<br />

LIBRARY IEEE;<br />

USE IEEE.STD_LOGIC_1164.ALL;<br />

USE IEEE.STD_LOGIC_TEXTIO.ALL;<br />

USE STD.TEXTIO.ALL;<br />

ENTITY tb_3pin IS<br />

END tb_3pin;<br />

--------------------------------------------------------------<br />

ARCHITECTURE arch_tb_3pin OF tb_3pin IS<br />

SIGNAL a,b,c,r,y: std_logic;<br />

COMPONENT mut_socket<br />

PORT (a,b,c: IN std_logic;<br />

END COMPONENT;<br />

y : OUT std_logic);<br />

FILE stimres : text OPEN read_mode IS "stimres";<br />

FILE errors : text OPEN write_mode IS "errors";<br />

BEGIN<br />

model_under_test: mut_socket PORT MAP (a,b,c,y);<br />

------------------------------------------------------------<br />

-- Stimulis und Antworten aus der Datei stimres lesen<br />

------------------------------------------------------------<br />

read_stimuli_and_responses: PROCESS<br />

VARIABLE Zeile : line;<br />

VARIABLE read_ok: boolean;<br />

VARIABLE Zeit : time;<br />

VARIABLE Signalname : character;<br />

VARIABLE space : character;<br />

VARIABLE data : std_logic;<br />

BEGIN<br />

WHILE NOT endfile(stimres) LOOP<br />

-- Lese Zeile<br />

READLINE (stimres, Zeile);<br />

<strong>VHDL</strong> - SIMULATION 108