Hardware-Entwurf mit VHDL

Hardware-Entwurf mit VHDL

Hardware-Entwurf mit VHDL

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

<strong>Hardware</strong>-<strong>Entwurf</strong> <strong>mit</strong> <strong>VHDL</strong><br />

Prof. Dr.-Ing. Stefan Wolter Elektrotechnik und Informatik<br />

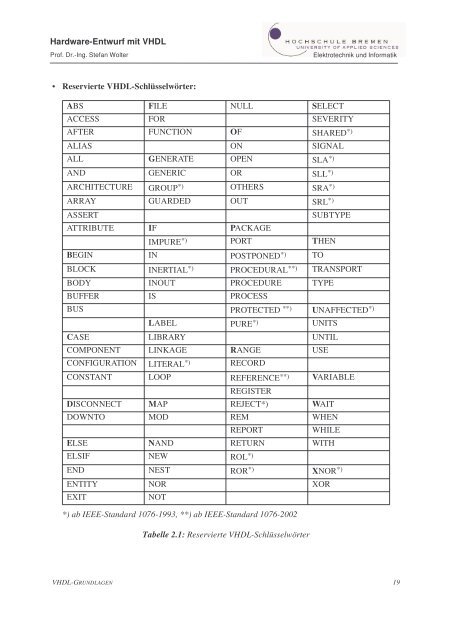

• Reservierte <strong>VHDL</strong>-Schlüsselwörter:<br />

ABS FILE NULL SELECT<br />

ACCESS FOR SEVERITY<br />

AFTER FUNCTION OF SHARED *)<br />

ALIAS ON SIGNAL<br />

ALL GENERATE OPEN SLA *)<br />

AND GENERIC OR SLL *)<br />

ARCHITECTURE GROUP *) OTHERS SRA *)<br />

ARRAY GUARDED OUT SRL *)<br />

ASSERT SUBTYPE<br />

ATTRIBUTE IF PACKAGE<br />

IMPURE *) PORT THEN<br />

BEGIN IN POSTPONED *) TO<br />

BLOCK INERTIAL *) PROCEDURAL **) TRANSPORT<br />

BODY INOUT PROCEDURE TYPE<br />

BUFFER IS PROCESS<br />

BUS PROTECTED **) UNAFFECTED *)<br />

LABEL PURE *) UNITS<br />

CASE LIBRARY UNTIL<br />

COMPONENT LINKAGE RANGE USE<br />

CONFIGURATION LITERAL *) RECORD<br />

CONSTANT LOOP REFERENCE **) VARIABLE<br />

REGISTER<br />

DISCONNECT MAP REJECT*) WAIT<br />

DOWNTO MOD REM WHEN<br />

REPORT WHILE<br />

ELSE NAND RETURN WITH<br />

ELSIF NEW ROL *)<br />

END NEST ROR *) XNOR *)<br />

ENTITY NOR XOR<br />

EXIT NOT<br />

*) ab IEEE-Standard 1076-1993, **) ab IEEE-Standard 1076-2002<br />

Tabelle 2.1: Reservierte <strong>VHDL</strong>-Schlüsselwörter<br />

<strong>VHDL</strong>-GRUNDLAGEN 19