Hardware-Entwurf mit VHDL

Hardware-Entwurf mit VHDL

Hardware-Entwurf mit VHDL

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

<strong>Hardware</strong>-<strong>Entwurf</strong> <strong>mit</strong> <strong>VHDL</strong><br />

Prof. Dr.-Ing. Stefan Wolter Elektrotechnik und Informatik<br />

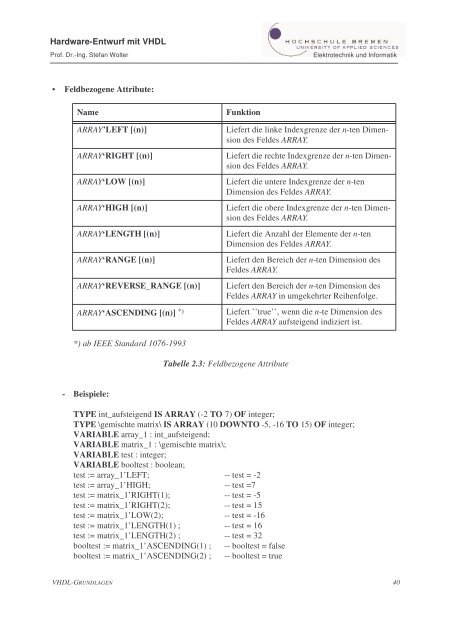

• Feldbezogene Attribute:<br />

Name Funktion<br />

ARRAY’LEFT [(n)] Liefert die linke Indexgrenze der n-ten Dimension<br />

des Feldes ARRAY.<br />

ARRAY‘RIGHT [(n)] Liefert die rechte Indexgrenze der n-ten Dimension<br />

des Feldes ARRAY.<br />

ARRAY‘LOW [(n)] Liefert die untere Indexgrenze der n-ten<br />

Dimension des Feldes ARRAY.<br />

ARRAY‘HIGH [(n)] Liefert die obere Indexgrenze der n-ten Dimension<br />

des Feldes ARRAY.<br />

ARRAY‘LENGTH [(n)] Liefert die Anzahl der Elemente der n-ten<br />

Dimension des Feldes ARRAY.<br />

ARRAY‘RANGE [(n)] Liefert den Bereich der n-ten Dimension des<br />

Feldes ARRAY.<br />

ARRAY‘REVERSE_RANGE [(n)] Liefert den Bereich der n-ten Dimension des<br />

Feldes ARRAY in umgekehrter Reihenfolge.<br />

ARRAY‘ASCENDING [(n)] *) Liefert ’’true’’, wenn die n-te Dimension des<br />

Feldes ARRAY aufsteigend indiziert ist.<br />

*) ab IEEE Standard 1076-1993<br />

- Beispiele:<br />

Tabelle 2.3: Feldbezogene Attribute<br />

TYPE int_aufsteigend IS ARRAY (-2 TO 7) OF integer;<br />

TYPE \gemischte matrix\ IS ARRAY (10 DOWNTO -5, -16 TO 15) OF integer;<br />

VARIABLE array_1 : int_aufsteigend;<br />

VARIABLE matrix_1 : \gemischte matrix\;<br />

VARIABLE test : integer;<br />

VARIABLE booltest : boolean;<br />

test := array_1’LEFT; -- test = -2<br />

test := array_1’HIGH; -- test =7<br />

test := matrix_1’RIGHT(1); -- test = -5<br />

test := matrix_1’RIGHT(2); -- test = 15<br />

test := matrix_1’LOW(2); -- test = -16<br />

test := matrix_1’LENGTH(1) ; -- test = 16<br />

test := matrix_1’LENGTH(2) ; -- test = 32<br />

booltest := matrix_1’ASCENDING(1) ; -- booltest = false<br />

booltest := matrix_1’ASCENDING(2) ; -- booltest = true<br />

<strong>VHDL</strong>-GRUNDLAGEN 40