Hardware-Entwurf mit VHDL

Hardware-Entwurf mit VHDL

Hardware-Entwurf mit VHDL

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

<strong>Hardware</strong>-<strong>Entwurf</strong> <strong>mit</strong> <strong>VHDL</strong><br />

Prof. Dr.-Ing. Stefan Wolter Elektrotechnik und Informatik<br />

Beispiel:<br />

SIGNAL b : signed (7 DOWNTO 0);<br />

SIGNAL a : unsigned (7 DOWNTO 0);<br />

Die erste Deklaration erzeugt ein Objekt <strong>mit</strong> einem Wertebereich von -128 bis + 127, während bei der<br />

zweiten Deklaration der Bereich 0 bis 255 ist.<br />

Eine wichtige Randbedingung für die Datentypen unsigned und signed ist, dass Felder stets von links<br />

nach rechts gelesen werden. Dabei steht das MSB immer links, unabhängig von der Indizierungsrichtung<br />

des Feldes. Aus diesem Grund wird empfohlen, dass die Indizierungsrichtung für diese Typen<br />

immer abfallend ist und das LSB immer den Index Null hat.<br />

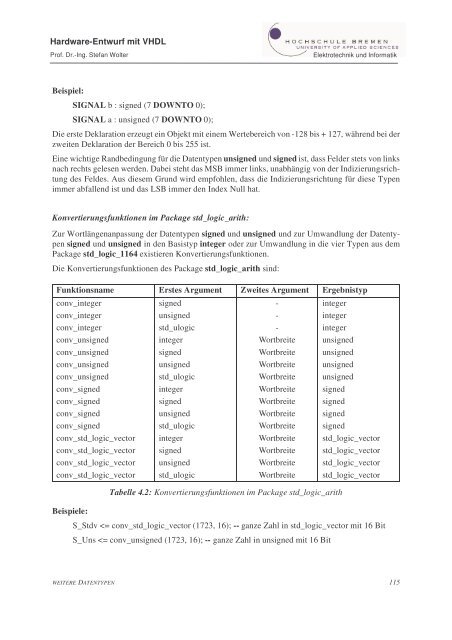

Konvertierungsfunktionen im Package std_logic_arith:<br />

Zur Wortlängenanpassung der Datentypen signed und unsigned und zur Umwandlung der Datentypen<br />

signed und unsigned in den Basistyp integer oder zur Umwandlung in die vier Typen aus dem<br />

Package std_logic_1164 existieren Konvertierungsfunktionen.<br />

Die Konvertierungsfunktionen des Package std_logic_arith sind:<br />

Funktionsname Erstes Argument Zweites Argument Ergebnistyp<br />

conv_integer<br />

conv_integer<br />

conv_integer<br />

conv_unsigned<br />

conv_unsigned<br />

conv_unsigned<br />

conv_unsigned<br />

conv_signed<br />

conv_signed<br />

conv_signed<br />

conv_signed<br />

conv_std_logic_vector<br />

conv_std_logic_vector<br />

conv_std_logic_vector<br />

conv_std_logic_vector<br />

Beispiele:<br />

signed<br />

unsigned<br />

std_ulogic<br />

integer<br />

signed<br />

unsigned<br />

std_ulogic<br />

integer<br />

signed<br />

unsigned<br />

std_ulogic<br />

integer<br />

signed<br />

unsigned<br />

std_ulogic<br />

-<br />

-<br />

-<br />

Wortbreite<br />

Wortbreite<br />

Wortbreite<br />

Wortbreite<br />

Wortbreite<br />

Wortbreite<br />

Wortbreite<br />

Wortbreite<br />

Wortbreite<br />

Wortbreite<br />

Wortbreite<br />

Wortbreite<br />

Tabelle 4.2: Konvertierungsfunktionen im Package std_logic_arith<br />

S_Stdv