Hardware-Entwurf mit VHDL

Hardware-Entwurf mit VHDL

Hardware-Entwurf mit VHDL

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

<strong>Hardware</strong>-<strong>Entwurf</strong> <strong>mit</strong> <strong>VHDL</strong><br />

Prof. Dr.-Ing. Stefan Wolter Elektrotechnik und Informatik<br />

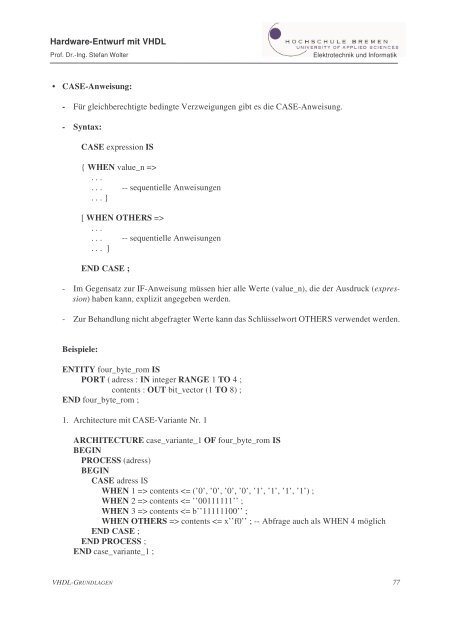

• CASE-Anweisung:<br />

- Für gleichberechtigte bedingte Verzweigungen gibt es die CASE-Anweisung.<br />

- Syntax:<br />

CASE expression IS<br />

{ WHEN value_n =><br />

. . .<br />

. . . -- sequentielle Anweisungen<br />

. . . }<br />

[ WHEN OTHERS =><br />

. . .<br />

. . . -- sequentielle Anweisungen<br />

. . . ]<br />

END CASE ;<br />

- Im Gegensatz zur IF-Anweisung müssen hier alle Werte (value_n), die der Ausdruck (expression)<br />

haben kann, explizit angegeben werden.<br />

- Zur Behandlung nicht abgefragter Werte kann das Schlüsselwort OTHERS verwendet werden.<br />

Beispiele:<br />

ENTITY four_byte_rom IS<br />

PORT ( adress : IN integer RANGE 1 TO 4 ;<br />

contents : OUT bit_vector (1 TO 8) ;<br />

END four_byte_rom ;<br />

1. Architecture <strong>mit</strong> CASE-Variante Nr. 1<br />

ARCHITECTURE case_variante_1 OF four_byte_rom IS<br />

BEGIN<br />

PROCESS (adress)<br />

BEGIN<br />

CASE adress IS<br />

WHEN 1 => contents contents contents contents