TI486 Microprocessor - Al Kossow's Bitsavers

TI486 Microprocessor - Al Kossow's Bitsavers

TI486 Microprocessor - Al Kossow's Bitsavers

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

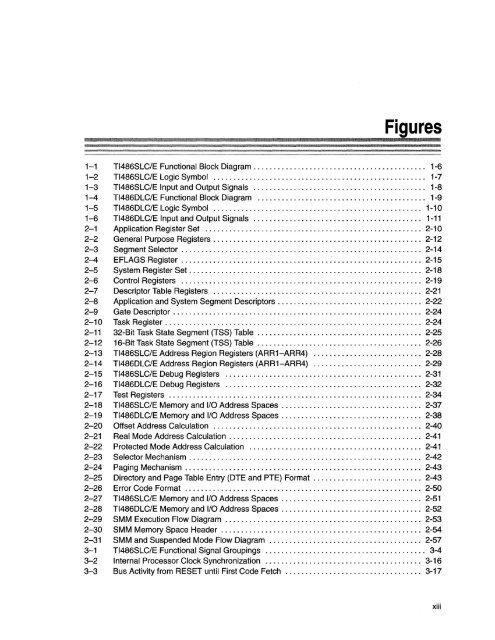

1-1 <strong>TI486</strong>SLC/E Functional Block Diagram .......................................... , 1-6<br />

1-2 <strong>TI486</strong>SLC/E Logic Symbol ..................................................... 1-7<br />

1-3 <strong>TI486</strong>SLC/E Input and Output Signals ........................................... 1-8<br />

1-4 <strong>TI486</strong>DLC/E Functional Block Diagram .......................................... 1-9<br />

1-5 <strong>TI486</strong>DLC/E Logic Symbol .................................................... 1-10<br />

1-6 <strong>TI486</strong>DLC/E Input and Output Signals .......................................... 1-11<br />

2-1 Application Register Set ...................................................... 2-10<br />

2-2 General Purpose Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 2-12<br />

2-3 Segment Selector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 2-14<br />

2-4 EFLAGS Register ............................. '" ... , ............ , ............ 2-15<br />

2-5 System Register Set. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 2-18<br />

2-6 Control Registers ............................................................ 2-19<br />

2-7 Descriptor Table Registers .................................................... 2-21<br />

2-8 Application and System Segment Descriptors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 2-22<br />

2-9 Gate Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 2-24<br />

2-10 Task Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 2-24<br />

2-11 32-Bit Task State Segment (TSS) Table .................................. . . . . . .. 2-25<br />

2-12 16-Bit Task State Segment (TSS) Table ......................................... 2-26<br />

2-13 <strong>TI486</strong>SLC/E Address Region Registers (ARR1-ARR4) ........................... 2-28<br />

2-14 <strong>TI486</strong>DLC/E Address Region Registers (ARR1-ARR4) ........................... 2-29<br />

2-15 <strong>TI486</strong>SLC/E Debug Registers ................................................. 2-31<br />

2-16 <strong>TI486</strong>DLC/E Debug Registers ................................................. 2-32<br />

2-17 Test Registers ............................................................... 2-34<br />

2-18 <strong>TI486</strong>SLC/E Memory and 1/0 Address Spaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 2-37<br />

2-19 <strong>TI486</strong>DLC/E Memory and 1/0 Address Spaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 2-38<br />

2-20 Offset Address Calculation .................................................... 2-40<br />

2-21 Real Mode Address Calculation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 2-41<br />

2-22 Protected Mode Address Calculation ........................................... 2-41<br />

2-23 Selector Mechanism . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 2-42<br />

2-24 Paging Mechanism . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 2-43<br />

2-25 Directory and Page Table Entry (DTE and PTE) Format .................... . . . . . .. 2-43<br />

2-26 Error Code Format ........................................................... 2-50<br />

2-27 <strong>TI486</strong>SLC/E Memory and 1/0 Address Spaces .......... , ........... , ...... , ..... 2-51<br />

2-28 <strong>TI486</strong>DLC/E Memory and 1/0 Address Spaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 2-52<br />

2-29 SMM Execution Flow Diagram ................................................. 2-53<br />

2-30 SMM Memory Space Header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 2-54<br />

2-31 SMM and Suspended Mode Flow Diagram ...................................... 2-57<br />

3-1 <strong>TI486</strong>SLC/E Functional Signal Groupings ........................................ 3-4<br />

3-2 Internal Processor Clock Synchronization ....................................... 3-16<br />

3-3 Bus Activity from RESET until First Code Fetch .................................. 3-17<br />

xiii