TI486 Microprocessor - Al Kossow's Bitsavers

TI486 Microprocessor - Al Kossow's Bitsavers

TI486 Microprocessor - Al Kossow's Bitsavers

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

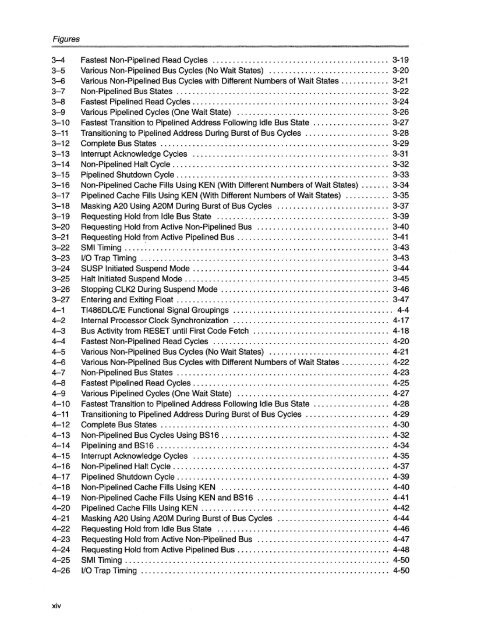

Figures<br />

3-4 Fastest Non-Pipelined Read Cycles ............................................ 3-19<br />

3-5 Various Non-Pipelined Bus Cycles (No Wait States) .............................. 3-20<br />

3-6 Various Non-Pipelined Bus Cycles with Different Numbers of Wait States. . . . . . . . . . .. 3-21<br />

3-7 Non-Pipelined Bus States ..................................................... 3-22<br />

3-8 Fastest Pipelined Read Cycles. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 3-24<br />

3-9 Various Pipelined Cycles (One Wait State) ...................................... 3-26<br />

3-10 Fastest Transition to Pipelined Address Following Idle Bus State ................... 3-27<br />

3-11 Transitioning to Pipelined Address During Burst of Bus Cycles ..................... 3-28<br />

3-12 Complete Bus States ......................................................... 3-29<br />

3-13 Interrupt Acknowledge Cycles ................................................. 3-31<br />

3-14 Non-Pipelined Halt Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 3-32<br />

3-15 Pipelined Shutdown Cycle. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 3-33<br />

3-16 Non-Pipelined Cache Fills Using KEN (With Different Numbers of Wait States) ....... 3-34<br />

3-17 Pipelined Cache Fills Using KEN (With Different Numbers of Wait States) ........... 3-35<br />

3-18 Masking A20 Using A20M During Burst of Bus Cycles ............................ 3-37<br />

3-19 Requesting Hold from Idle Bus State ........................................... 3-39<br />

3-20 Requesting Hold from Active Non-Pipelined Bus ................................. 3-40<br />

3-21 Requesting Hold f,rom Active Pipelined Bus ...................................... 3-41<br />

3-22 SMI Timing .................................................................. 3-43<br />

3-23 liD Trap Timing .............................................................. 3-43<br />

3-24 SUSP Initiated Suspend Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 3-44<br />

3-25 Halt Initiated Suspend Mode ....... , ..................... , ..................... 3-45<br />

3-26 Stopping CLK2 During Suspend Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 3-46<br />

3-27 Entering and Exiting Float ..................................................... 3-47<br />

4-1 <strong>TI486</strong>DLC/E Functional Signal Groupings ... " ....... , .. " ., .................... , 4-4<br />

4-2 Internal Processor Clock Synchronization ....................................... 4-17<br />

4-3 Bus Activity from RESET until First Code Fetch .................................. 4-18<br />

4-4 Fastest Non-Pipelined Read Cycles ............................................ 4-20<br />

4-5 Various Non-Pipelined Bus Cycles (No Wait States) .............................. 4-21<br />

4-6 Various Non-Pipelined Bus Cycles with Different Numbers of Wait States. . . . . . . . . . .. 4-22<br />

4-7 Non-Pipelined Bus States .... " .... " ........... , ..... " ... '" ... , ...... " .... 4-23<br />

4-8 Fastest Pipelined Read Cycles. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 4-25<br />

4-9 Various Pipelined Cycles (One Wait State) ...................................... 4-27<br />

4-10 Fastest Transition to Pipelined Address Following Idle Bus State ................... 4-28<br />

4-11 Transitioning to Pipelined Address During Burst of Bus Cycles ..................... 4-29<br />

4-12 Complete Bus States ......................................................... 4-30<br />

4-13 Non-Pipelined Bus Cycles Using BS 16 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 4-32<br />

4-14 Pipelining and BS 16 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 4-34<br />

4-15 Interrupt Acknowledge Cycles ................................................. 4-35<br />

4-16 Non-Pipelined Halt Cycle. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 4-37<br />

4-17 Pipelined Shutdown Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 4-39<br />

4-18 Non-Pipelined Cache Fills Using KEN .......................................... 4-40<br />

4-19 Non-Pipelined Cache Fills Using KEN and BS16 ................................. 4-41<br />

4-20 Pipelined Cache Fills Using KEN .............................................. , 4-42<br />

4-21 Masking A20 Using A20M During Burst of Bus Cycles ............................ 4-44<br />

4-22 Requesting Hold from Idle Bus State ........................................... 4-46<br />

4-23 Requesting Hold from Active Non-Pipelined Bus ................................. 4-47<br />

4-24 Requesting Hold from Active Pipelined Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 4-48<br />

4-25 SMI Timing .................................................................. 4-50<br />

4-26 liD Trap Timing .............................................................. 4-50<br />

xiv