- Seite 1 und 2:

Schaltungsdesign mit VHDL Gunther L

- Seite 3 und 4:

Vorwort VHDL1 ist ein weltweit akze

- Seite 5 und 6:

Vorwort In dem vorliegenden Buch is

- Seite 7 und 8:

Zu diesem Buch Als eine der wenigen

- Seite 9 und 10:

Inhalt Teil A Einführung 1 Entwurf

- Seite 11 und 12:

Inhalt 6.3 Signalzuweisungen und Ve

- Seite 13 und 14:

Teil A Einführung © G. Lehmann/B.

- Seite 15 und 16:

1 Entwurf elektronischer Systeme ti

- Seite 17 und 18:

1.3.2 Algorithmische Ebene 1 Entwur

- Seite 19 und 20:

1 Entwurf elektronischer Systeme st

- Seite 21 und 22:

2 Motivation für eine normierte Ha

- Seite 23 und 24:

2 Motivation für eine normierte Ha

- Seite 25 und 26:

3 Geschichtliche Entwicklung von VH

- Seite 27 und 28:

4 Aufbau einer VHDL- Beschreibung D

- Seite 29 und 30:

4 Aufbau einer VHDL-Beschreibung Vo

- Seite 31 und 32:

5 Entwurfssichten in VHDL Im vorges

- Seite 33 und 34:

Eine entsprechende Architektur für

- Seite 35 und 36:

6 Entwurfsebenen in VHDL Die weiten

- Seite 37 und 38:

6 Entwurfsebenen in VHDL setzt, dam

- Seite 39 und 40:

7.1.1 Erfassung der Spezifikation 7

- Seite 41 und 42:

7.1.6 Layouterzeugung und Produktio

- Seite 43 und 44:

7.2.4 Syntheseprogramme 7 Design-Me

- Seite 45 und 46:

Technologie A (FPGAs) Hersteller 1

- Seite 47 und 48:

8 Bewertung von VHDL Durch Kombinat

- Seite 49 und 50:

8 Bewertung von VHDL Aktuelle Bestr

- Seite 51 und 52:

Teil B Die Sprache VHDL © G. Lehma

- Seite 53 und 54:

1.2 Vorgehensweise und Nomenklatur

- Seite 55 und 56:

2.2 Zeichensatz 2 Sprachelemente De

- Seite 57 und 58:

2 Sprachelemente Damit VHDL-Modelle

- Seite 59 und 60:

2 Sprachelemente p sie dürfen Leer

- Seite 61 und 62:

2.3.4.1 Numerische Größen 2 Sprac

- Seite 63 und 64:

2.3.4.2 Zeichengrößen 2 Sprachele

- Seite 65 und 66:

2 Sprachelemente Als Trenn- und Beg

- Seite 67 und 68:

2 Sprachelemente Gruppen mit gleich

- Seite 69 und 70:

3 Objekte Sämtliche Daten in VHDL

- Seite 71 und 72:

3 Objekte ... a := 0.4; -- "real-Va

- Seite 73 und 74:

3 Objekte Der maximal mögliche Wer

- Seite 75 und 76:

Der einzige vordefinierte, physikal

- Seite 77 und 78:

integer (float_object_name) real (i

- Seite 79 und 80:

TYPE string IS ARRAY (positive RANG

- Seite 81 und 82:

3 Objekte Mit 393 kann der Name des

- Seite 83 und 84:

3 Objekte p im BLOCK-Deklarationste

- Seite 85 und 86:

3 Objekte dabei mitunter auf ein- u

- Seite 87 und 88:

3.4 Ansprechen von Objekten 3.4.1 O

- Seite 89 und 90:

3 Objekte PROCESS VARIABLE v_1, v_2

- Seite 91 und 92:

3 Objekte Die Zuweisung von komplet

- Seite 93 und 94:

4 Aufbau eines VHDL-Modells stimmte

- Seite 95 und 96:

4 Aufbau eines VHDL-Modells USE lib

- Seite 97 und 98:

4 Aufbau eines VHDL-Modells Die opt

- Seite 99 und 100:

4 Aufbau eines VHDL-Modells d.h. di

- Seite 101 und 102:

4 Aufbau eines VHDL-Modells damit w

- Seite 103 und 104:

Package Body Package 4 Aufbau eines

- Seite 105 und 106:

5 Strukturale Modellierung ARCHITEC

- Seite 107 und 108:

5 Strukturale Modellierung COMPONEN

- Seite 109 und 110:

5 Strukturale Modellierung ARCHITEC

- Seite 111 und 112:

5 Strukturale Modellierung Natürli

- Seite 113 und 114:

5 Strukturale Modellierung ARCHITEC

- Seite 115 und 116:

ARCHITECTURE structural OF n_bit_re

- Seite 117 und 118:

6 Verhaltensmodellierung Im vorange

- Seite 119 und 120:

6.1 Operatoren 6 Verhaltensmodellie

- Seite 121 und 122:

6.1.2 Vergleichsoperatoren Operator

- Seite 123 und 124:

6.1.3 Arithmetische Operatoren 6.1.

- Seite 125 und 126:

6.1.3.3 Multiplizierende Operatoren

- Seite 127 und 128:

Operator Funktion Typ linker Operan

- Seite 129 und 130:

Name Funktion 6 Verhaltensmodellier

- Seite 131 und 132:

6 Verhaltensmodellierung und PRED/S

- Seite 133 und 134:

6 Verhaltensmodellierung s'QUIET [(

- Seite 135 und 136:

Mit 393 sind weitere signalbezogene

- Seite 137 und 138:

6.3 Signalzuweisungen und Verzöger

- Seite 139 und 140:

6 Verhaltensmodellierung nicht änd

- Seite 141 und 142:

6 Verhaltensmodellierung eingeführ

- Seite 143 und 144:

6.4 Nebenläufige Anweisungen 6 Ver

- Seite 145 und 146:

ENTITY latch IS PORT (d, clk : IN b

- Seite 147 und 148:

eset_check : ASSERT sig_reset /= '0

- Seite 149 und 150:

6 Verhaltensmodellierung und Signal

- Seite 151 und 152:

6 Verhaltensmodellierung im Ausfüh

- Seite 153 und 154:

6 Verhaltensmodellierung Die einzel

- Seite 155 und 156:

6 Verhaltensmodellierung Mit der ü

- Seite 157 und 158:

ARCHITECTURE case_variante_2 OF fou

- Seite 159 und 160: 6 Verhaltensmodellierung Die Schlei

- Seite 161 und 162: ARCHITECTURE behavioral OF n_time_l

- Seite 163 und 164: 6.6.1 Funktionen 6 Verhaltensmodell

- Seite 165 und 166: 6 Verhaltensmodellierung Die Verein

- Seite 167 und 168: 6 Verhaltensmodellierung Die oben d

- Seite 169 und 170: PROCEDURE hello; PROCEDURE d_ff ( C

- Seite 171 und 172: 6 Verhaltensmodellierung nicht ange

- Seite 173 und 174: 6 Verhaltensmodellierung ARCHITECTU

- Seite 175 und 176: 7 Konfigurieren von VHDL-Modellen 7

- Seite 177 und 178: 7 Konfigurieren von VHDL-Modellen W

- Seite 179 und 180: 7 Konfigurieren von VHDL-Modellen W

- Seite 181 und 182: CONFIGURATION ha_config OF halfadde

- Seite 183 und 184: 7 Konfigurieren von VHDL-Modellen D

- Seite 185 und 186: 8 Simulationsablauf Signalzuweisung

- Seite 187 und 188: 8 Simulationsablauf ARCHITECTURE nu

- Seite 189 und 190: 8.3.1 Prozesse 8 Simulationsablauf

- Seite 191 und 192: 9 Besonderheiten bei Signalen Neben

- Seite 193 und 194: 9 Besonderheiten bei Signalen Die A

- Seite 195 und 196: 9 Besonderheiten bei Signalen ARCHI

- Seite 197 und 198: 9 Besonderheiten bei Signalen Die Z

- Seite 199 und 200: 10 Gültigkeit und Sichtbarkeit Um

- Seite 201 und 202: 10 Gültigkeit und Sichtbarkeit spr

- Seite 203 und 204: 11 Spezielle Modellierungstechniken

- Seite 205 und 206: 11.2 Gruppen 393 11 Spezielle Model

- Seite 207 und 208: 11.3 Überladung 11 Spezielle Model

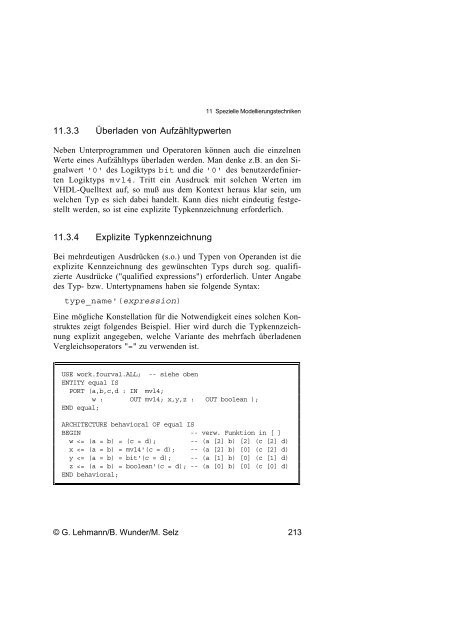

- Seite 209: 11 Spezielle Modellierungstechniken

- Seite 213 und 214: Entity Komp.-instanz Architektur 11

- Seite 215 und 216: 11.5.1 Typspezifische Files 11 Spez

- Seite 217 und 218: 11 Spezielle Modellierungstechniken

- Seite 219 und 220: 11.5.3 Handhabung von Files in 393

- Seite 221 und 222: 11 Spezielle Modellierungstechniken

- Seite 223 und 224: element_data next_element element_d

- Seite 225 und 226: 11 Spezielle Modellierungstechniken

- Seite 227 und 228: Teil C Anwendung von VHDL © G. Leh

- Seite 229 und 230: 1 Simulation tax-Checkern durchgef

- Seite 231 und 232: 1.2.3 Native-Compiled Simulationste

- Seite 233 und 234: 1 Simulation auch dazu verwendet we

- Seite 235 und 236: 1 Simulation ARCHITECTURE strategy_

- Seite 237 und 238: 1 Simulation -------- Fortsetzung v

- Seite 239 und 240: 1 Simulation wurde bereits eine tec

- Seite 241 und 242: 2 Synthese strukturen beschrieben.

- Seite 243 und 244: 2 Synthese Die Register-Transfer-Sy

- Seite 245 und 246: p Vor dem Structuring: f = (a ∧ d

- Seite 247 und 248: 2 Synthese stützen, da bei der Anw

- Seite 249 und 250: 2 Synthese Im folgenden soll deshal

- Seite 251 und 252: 2 Synthese Die folgenden beiden Arc

- Seite 253 und 254: 2 Synthese ergeben sich zuerst aufg

- Seite 255 und 256: 2 Synthese Bei der Architektur fals

- Seite 257 und 258: ARCHITECTURE cla OF addierer IS SIG

- Seite 259 und 260: 2 Synthese ARCHITECTURE eins OF bar

- Seite 261 und 262:

2.4 Synthese von sequentiellen Scha

- Seite 263 und 264:

ARCHITECTURE variante2 OF dff IS BE

- Seite 265 und 266:

ENTITY dff IS PORT (clk,d,reset: IN

- Seite 267 und 268:

2 Synthese Da die Prozesse zur Besc

- Seite 269 und 270:

Laufzeit / [ns] 8 7 6 5 4 3 120 130

- Seite 271 und 272:

2 Synthese Eine neunfache Optimieru

- Seite 273 und 274:

Rechenzeit / [sec] Rechenzeit / [se

- Seite 275 und 276:

Teil D Anhang © G. Lehmann/B. Wund

- Seite 277 und 278:

1 Packages p Multiplikations- und D

- Seite 279 und 280:

1 Packages Bei Objekten des Typs ti

- Seite 281 und 282:

1 Packages Am Beispiel des Operator

- Seite 283 und 284:

Die Auflösungsfunktion wird folgen

- Seite 285 und 286:

1 Packages Als Beispiel einer Funkt

- Seite 287 und 288:

2.1.2 Strukturale Modellierung 2 VH

- Seite 289 und 290:

2 VHDL-Übungsbeispiele p Gegeben s

- Seite 291 und 292:

2 VHDL-Übungsbeispiele Segment leu

- Seite 293 und 294:

2 VHDL-Übungsbeispiele zweites Fil

- Seite 295 und 296:

2 VHDL-Übungsbeispiele Diese Funkt

- Seite 297 und 298:

3.2 VHDL International 3 VHDL-Gremi

- Seite 299 und 300:

Herausgeber: Jaques Rouillard und J

- Seite 301 und 302:

4 Disketteninhalt Dem Buch liegt ei

- Seite 303 und 304:

Literatur Die im folgenden aufgefü

- Seite 305 und 306:

[GUY 92] A. Guyler: "VHDL 1076-1992

- Seite 307 und 308:

[SEL 93d] M. Selz, K. D. Müller-Gl

- Seite 309 und 310:

Sachverzeichnis Die im folgenden au

- Seite 311 und 312:

FOR 154; 160; 177 FOREIGN 228 forma

- Seite 313 und 314:

PROCEDURE, Prozeduren 163; 170; 192

- Seite 315 und 316:

Unvollständige Typdeklarationen 22