Etude de la fiabilité porteurs chauds et des performances des ...

Etude de la fiabilité porteurs chauds et des performances des ...

Etude de la fiabilité porteurs chauds et des performances des ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

tel-00117263, version 2 - 29 Jan 2007<br />

Thierry DI GILIO<br />

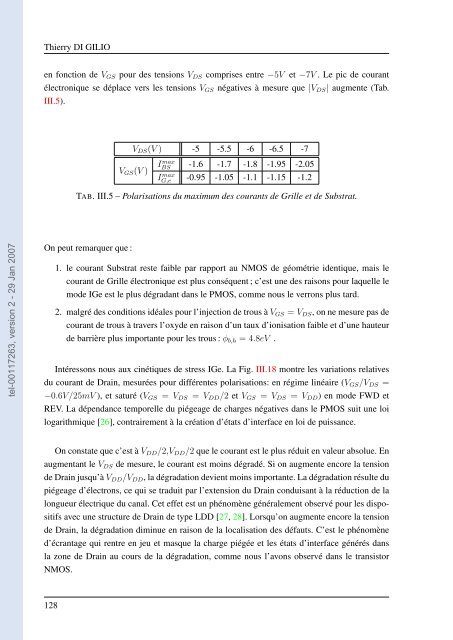

en fonction <strong>de</strong> VGS pour <strong>de</strong>s tensions VDS comprises entre −5V <strong>et</strong> −7V . Le pic <strong>de</strong> courant<br />

électronique se dép<strong>la</strong>ce vers les tensions VGS négatives à mesure que |VDS| augmente (Tab.<br />

III.5).<br />

VDS(V ) -5 -5.5 -6 -6.5 -7<br />

VGS(V )<br />

I max<br />

BS -1.6 -1.7 -1.8 -1.95 -2.05<br />

I max<br />

G,e -0.95 -1.05 -1.1 -1.15 -1.2<br />

TAB. III.5 – Po<strong>la</strong>risations du maximum <strong>de</strong>s courants <strong>de</strong> Grille <strong>et</strong> <strong>de</strong> Substrat.<br />

On peut remarquer que :<br />

1. le courant Substrat reste faible par rapport au NMOS <strong>de</strong> géométrie i<strong>de</strong>ntique, mais le<br />

courant <strong>de</strong> Grille électronique est plus conséquent ; c’est une <strong>de</strong>s raisons pour <strong>la</strong>quelle le<br />

mo<strong>de</strong> IGe est le plus dégradant dans le PMOS, comme nous le verrons plus tard.<br />

2. malgré <strong>de</strong>s conditions idéales pour l’injection <strong>de</strong> trous à VGS = VDS, on ne mesure pas <strong>de</strong><br />

courant <strong>de</strong> trous à travers l’oxy<strong>de</strong> en raison d’un taux d’ionisation faible <strong>et</strong> d’une hauteur<br />

<strong>de</strong> barrière plus importante pour les trous : φb,h = 4.8eV .<br />

Intéressons nous aux cinétiques <strong>de</strong> stress IGe. La Fig. III.18 montre les variations re<strong>la</strong>tives<br />

du courant <strong>de</strong> Drain, mesurées pour différentes po<strong>la</strong>risations: en régime linéaire (VGS/VDS =<br />

−0.6V/25mV ), <strong>et</strong> saturé (VGS = VDS = VDD/2 <strong>et</strong> VGS = VDS = VDD) en mo<strong>de</strong> FWD <strong>et</strong><br />

REV. La dépendance temporelle du piégeage <strong>de</strong> charges négatives dans le PMOS suit une loi<br />

logarithmique [26], contrairement à <strong>la</strong> création d’états d’interface en loi <strong>de</strong> puissance.<br />

On constate que c’est à VDD/2,VDD/2 que le courant est le plus réduit en valeur absolue. En<br />

augmentant le VDS <strong>de</strong> mesure, le courant est moins dégradé. Si on augmente encore <strong>la</strong> tension<br />

<strong>de</strong> Drain jusqu’à VDD/VDD, <strong>la</strong> dégradation <strong>de</strong>vient moins importante. La dégradation résulte du<br />

piégeage d’électrons, ce qui se traduit par l’extension du Drain conduisant à <strong>la</strong> réduction <strong>de</strong> <strong>la</strong><br />

longueur électrique du canal. C<strong>et</strong> eff<strong>et</strong> est un phénomène généralement observé pour les dispo-<br />

sitifs avec une structure <strong>de</strong> Drain <strong>de</strong> type LDD [27, 28]. Lorsqu’on augmente encore <strong>la</strong> tension<br />

<strong>de</strong> Drain, <strong>la</strong> dégradation diminue en raison <strong>de</strong> <strong>la</strong> localisation <strong>de</strong>s défauts. C’est le phénomène<br />

d’écrantage qui rentre en jeu <strong>et</strong> masque <strong>la</strong> charge piégée <strong>et</strong> les états d’interface générés dans<br />

<strong>la</strong> zone <strong>de</strong> Drain au cours <strong>de</strong> <strong>la</strong> dégradation, comme nous l’avons observé dans le transistor<br />

NMOS.<br />

128