(SCI) - Technologie und Leistungsanalysen.pdf

(SCI) - Technologie und Leistungsanalysen.pdf

(SCI) - Technologie und Leistungsanalysen.pdf

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Teststand wurden NWRITE64 <strong>und</strong> NREAD64-Transaktionen für die Messungen<br />

verwendet, bei beide 64 Byte pro Paket verschicken, während beim zweiten<br />

Teststand DMOVE64-Transaktionen herangezogen wurden, die zwar die gleiche<br />

Paketlänge aufweisen jedoch keine Response benötigen.<br />

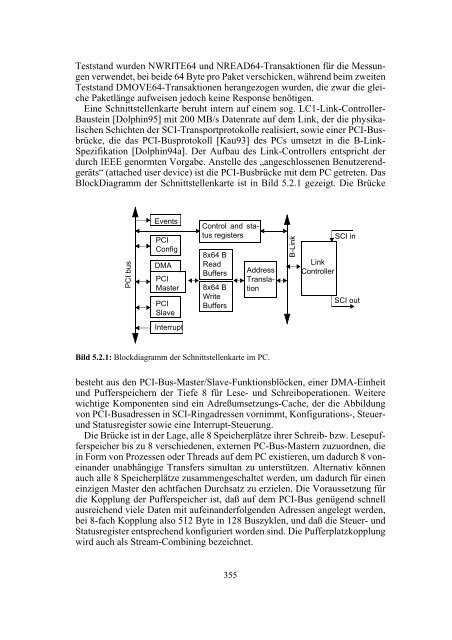

Eine Schnittstellenkarte beruht intern auf einem sog. LC1-Link-Controller-<br />

Baustein [Dolphin95] mit 200 MB/s Datenrate auf dem Link, der die physikalischen<br />

Schichten der <strong>SCI</strong>-Transportprotokolle realisiert, sowie einer PCI-Busbrücke,<br />

die das PCI-Busprotokoll [Kau93] des PCs umsetzt in die B-Link-<br />

Spezifikation [Dolphin94a]. Der Aufbau des Link-Controllers entspricht der<br />

durch IEEE genormten Vorgabe. Anstelle des „angeschlossenen Benutzerendgeräts“<br />

(attached user device) ist die PCI-Busbrücke mit dem PC getreten. Das<br />

BlockDiagramm der Schnittstellenkarte ist in Bild 5.2.1 gezeigt. Die Brücke<br />

PCI bus<br />

Events<br />

PCI<br />

Config<br />

DMA<br />

PCI<br />

Master<br />

PCI<br />

Slave<br />

Control and status<br />

registers<br />

8x64 B<br />

Read<br />

Buffers<br />

8x64 B<br />

Write<br />

Buffers<br />

Address<br />

Translation<br />

B-Link<br />

Link<br />

Controller<br />

<strong>SCI</strong> in<br />

<strong>SCI</strong> out<br />

Interrupt<br />

Bild 5.2.1: Blockdiagramm der Schnittstellenkarte im PC.<br />

besteht aus den PCI-Bus-Master/Slave-Funktionsblöcken, einer DMA-Einheit<br />

<strong>und</strong> Pufferspeichern der Tiefe 8 für Lese- <strong>und</strong> Schreiboperationen. Weitere<br />

wichtige Komponenten sind ein Adreßumsetzungs-Cache, der die Abbildung<br />

von PCI-Busadressen in <strong>SCI</strong>-Ringadressen vornimmt, Konfigurations-, Steuer<strong>und</strong><br />

Statusregister sowie eine Interrupt-Steuerung.<br />

Die Brücke ist in der Lage, alle 8 Speicherplätze ihrer Schreib- bzw. Lesepufferspeicher<br />

bis zu 8 verschiedenen, externen PC-Bus-Mastern zuzuordnen, die<br />

in Form von Prozessen oder Threads auf dem PC existieren, um dadurch 8 voneinander<br />

unabhängige Transfers simultan zu unterstützen. Alternativ können<br />

auch alle 8 Speicherplätze zusammengeschaltet werden, um dadurch für einen<br />

einzigen Master den achtfachen Durchsatz zu erzielen. Die Voraussetzung für<br />

die Kopplung der Pufferspeicher ist, daß auf dem PCI-Bus genügend schnell<br />

ausreichend viele Daten mit aufeinanderfolgenden Adressen angelegt werden,<br />

bei 8-fach Kopplung also 512 Byte in 128 Buszyklen, <strong>und</strong> daß die Steuer- <strong>und</strong><br />

Statusregister entsprechend konfiguriert worden sind. Die Pufferplatzkopplung<br />

wird auch als Stream-Combining bezeichnet.<br />

355