Intel® 865G/865GV Chipset Datasheet - download.intel.nl - Intel

Intel® 865G/865GV Chipset Datasheet - download.intel.nl - Intel

Intel® 865G/865GV Chipset Datasheet - download.intel.nl - Intel

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

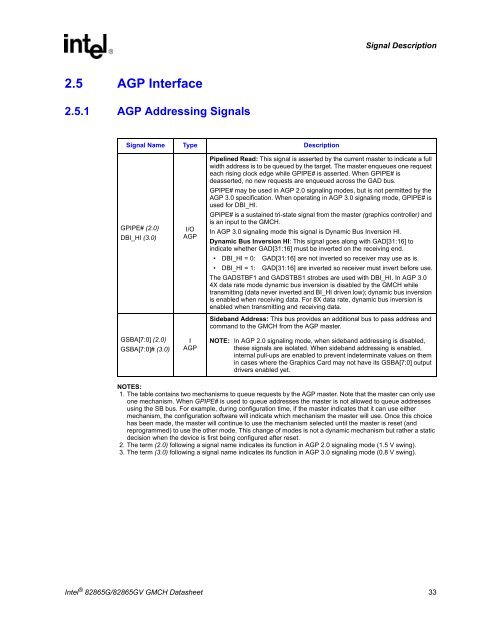

Signal Description2.5 AGP Interface2.5.1 AGP Addressing SignalsSignal Name Type DescriptionGPIPE# (2.0)DBI_HI (3.0)GSBA[7:0] (2.0)GSBA[7:0]# (3.0)I/OAGPIAGPPipelined Read: This signal is asserted by the current master to indicate a fullwidth address is to be queued by the target. The master enqueues one requesteach rising clock edge while GPIPE# is asserted. When GPIPE# isdeasserted, no new requests are enqueued across the GAD bus.GPIPE# may be used in AGP 2.0 signaling modes, but is not permitted by theAGP 3.0 specification. When operating in AGP 3.0 signaling mode, GPIPE# isused for DBI_HI.GPIPE# is a sustained tri-state signal from the master (graphics controller) andis an input to the GMCH.In AGP 3.0 signaling mode this signal is Dynamic Bus Inversion HI.Dynamic Bus Inversion HI: This signal goes along with GAD[31:16] toindicate whether GAD[31:16] must be inverted on the receiving end.• DBI_HI = 0: GAD[31:16] are not inverted so receiver may use as is.• DBI_HI = 1: GAD[31:16] are inverted so receiver must invert before use.The GADSTBF1 and GADSTBS1 strobes are used with DBI_HI. In AGP 3.04X data rate mode dynamic bus inversion is disabled by the GMCH whiletransmitting (data never inverted and BI_HI driven low); dynamic bus inversionis enabled when receiving data. For 8X data rate, dynamic bus inversion isenabled when transmitting and receiving data.Sideband Address: This bus provides an additional bus to pass address andcommand to the GMCH from the AGP master.NOTE: In AGP 2.0 signaling mode, when sideband addressing is disabled,these signals are isolated. When sideband addressing is enabled,internal pull-ups are enabled to prevent indeterminate values on themin cases where the Graphics Card may not have its GSBA[7:0] outputdrivers enabled yet.NOTES:1. The table contains two mechanisms to queue requests by the AGP master. Note that the master can o<strong>nl</strong>y useone mechanism. When GPIPE# is used to queue addresses the master is not allowed to queue addressesusing the SB bus. For example, during configuration time, if the master indicates that it can use eithermechanism, the configuration software will indicate which mechanism the master will use. Once this choicehas been made, the master will continue to use the mechanism selected until the master is reset (andreprogrammed) to use the other mode. This change of modes is not a dynamic mechanism but rather a staticdecision when the device is first being configured after reset.2. The term (2.0) following a signal name indicates its function in AGP 2.0 signaling mode (1.5 V swing).3. The term (3.0) following a signal name indicates its function in AGP 3.0 signaling mode (0.8 V swing).<strong>Intel</strong> ® 82<strong>865G</strong>/82<strong>865G</strong>V GMCH <strong>Datasheet</strong> 33