Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

R<br />

HOSTCLK<br />

HOSTMIIMSEL<br />

HOSTREQ<br />

HOSTOPCODE[1:0]<br />

HOSTADDR[9:0]<br />

HOSTWRDATA[15:0]<br />

HOSTMIIMRDY<br />

HOSTRDDATA[15:0]<br />

HOSTE<strong>MAC</strong>1SEL<br />

Using the DCR Bus<br />

Using the DCR Bus<br />

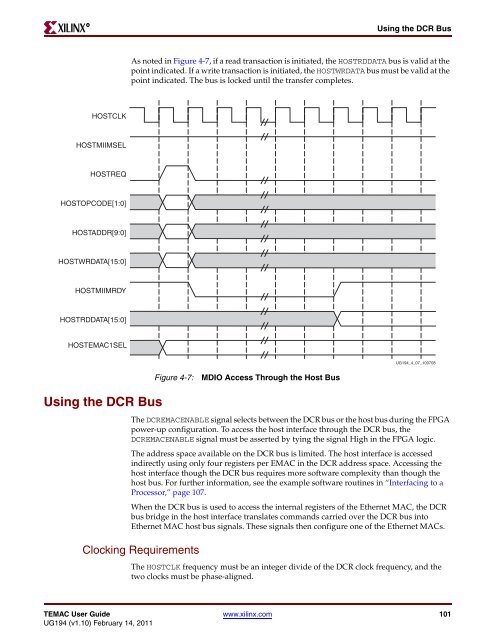

As noted in Figure 4-7, if a read transaction is initiated, the HOSTRDDATA bus is valid at the<br />

point indicated. If a write transaction is initiated, the HOSTWRDATA bus must be valid at the<br />

point indicated. The bus is locked until the transfer completes.<br />

The DCRE<strong>MAC</strong>ENABLE signal selects between the DCR bus or the host bus during the <strong>FPGA</strong><br />

power-up configuration. To access the host interface through the DCR bus, the<br />

DCRE<strong>MAC</strong>ENABLE signal must be asserted by tying the signal High in the <strong>FPGA</strong> logic.<br />

The address space available on the DCR bus is limited. The host interface is accessed<br />

indirectly using only four registers per E<strong>MAC</strong> in the DCR address space. Accessing the<br />

host interface though the DCR bus requires more software complexity than though the<br />

host bus. For further information, see the example software routines in “Interfacing to a<br />

Processor,” page 107.<br />

When the DCR bus is used to access the internal registers of the <strong>Ethernet</strong> <strong>MAC</strong>, the DCR<br />

bus bridge in the host interface translates commands carried over the DCR bus into<br />

<strong>Ethernet</strong> <strong>MAC</strong> host bus signals. These signals then configure one of the <strong>Ethernet</strong> <strong>MAC</strong>s.<br />

Clocking Requirements<br />

Figure 4-7: MDIO Access Through the Host Bus<br />

<strong>UG194</strong>_4_07_100708<br />

The HOSTCLK frequency must be an integer divide of the DCR clock frequency, and the<br />

two clocks must be phase-aligned.<br />

TE<strong>MAC</strong> User Guide www.xilinx.com 101<br />

<strong>UG194</strong> (v1.10) February 14, 2011