Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Chapter 2: <strong>Ethernet</strong> <strong>MAC</strong> Overview<br />

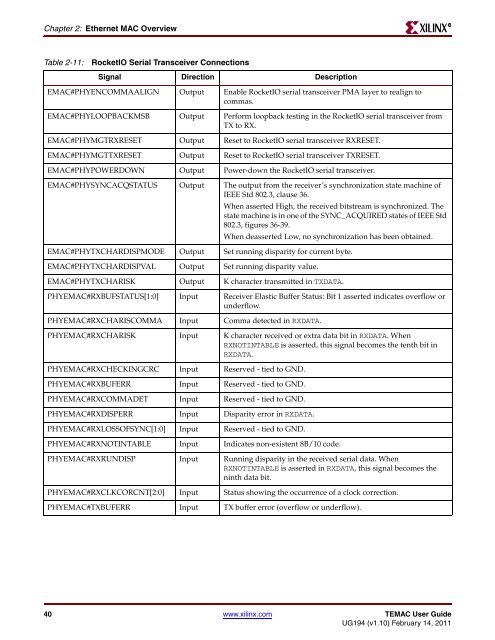

Table 2-11: RocketIO Serial Transceiver Connections<br />

Signal Direction Description<br />

E<strong>MAC</strong>#PHYENCOMMAALIGN Output Enable RocketIO serial transceiver PMA layer to realign to<br />

commas.<br />

E<strong>MAC</strong>#PHYLOOPBACKMSB Output Perform loopback testing in the RocketIO serial transceiver from<br />

TX to RX.<br />

E<strong>MAC</strong>#PHYMGTRXRESET Output Reset to RocketIO serial transceiver RXRESET.<br />

E<strong>MAC</strong>#PHYMGTTXRESET Output Reset to RocketIO serial transceiver TXRESET.<br />

E<strong>MAC</strong>#PHYPOWERDOWN Output Power-down the RocketIO serial transceiver.<br />

E<strong>MAC</strong>#PHYSYNCACQSTATUS Output The output from the receiver’s synchronization state machine of<br />

IEEE Std 802.3, clause 36.<br />

When asserted High, the received bitstream is synchronized. The<br />

state machine is in one of the SYNC_ACQUIRED states of IEEE Std<br />

802.3, figures 36-39.<br />

When deasserted Low, no synchronization has been obtained.<br />

E<strong>MAC</strong>#PHYTXCHARDISPMODE Output Set running disparity for current byte.<br />

E<strong>MAC</strong>#PHYTXCHARDISPVAL Output Set running disparity value.<br />

E<strong>MAC</strong>#PHYTXCHARISK Output K character transmitted in TXDATA.<br />

PHYE<strong>MAC</strong>#RXBUFSTATUS[1:0] Input Receiver Elastic Buffer Status: Bit 1 asserted indicates overflow or<br />

underflow.<br />

PHYE<strong>MAC</strong>#RXCHARISCOMMA Input Comma detected in RXDATA.<br />

PHYE<strong>MAC</strong>#RXCHARISK Input K character received or extra data bit in RXDATA. When<br />

RXNOTINTABLE is asserted, this signal becomes the tenth bit in<br />

RXDATA.<br />

PHYE<strong>MAC</strong>#RXCHECKINGCRC Input Reserved - tied to GND.<br />

PHYE<strong>MAC</strong>#RXBUFERR Input Reserved - tied to GND.<br />

PHYE<strong>MAC</strong>#RXCOMMADET Input Reserved - tied to GND.<br />

PHYE<strong>MAC</strong>#RXDISPERR Input Disparity error in RXDATA.<br />

PHYE<strong>MAC</strong>#RXLOSSOFSYNC[1:0] Input Reserved - tied to GND.<br />

PHYE<strong>MAC</strong>#RXNOTINTABLE Input Indicates non-existent 8B/10 code.<br />

PHYE<strong>MAC</strong>#RXRUNDISP Input Running disparity in the received serial data. When<br />

RXNOTINTABLE is asserted in RXDATA, this signal becomes the<br />

ninth data bit.<br />

PHYE<strong>MAC</strong>#RXCLKCORCNT[2:0] Input Status showing the occurrence of a clock correction.<br />

PHYE<strong>MAC</strong>#TXBUFERR Input TX buffer error (overflow or underflow).<br />

40 www.xilinx.com TE<strong>MAC</strong> User Guide<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

R