Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Chapter 3: Client Interface<br />

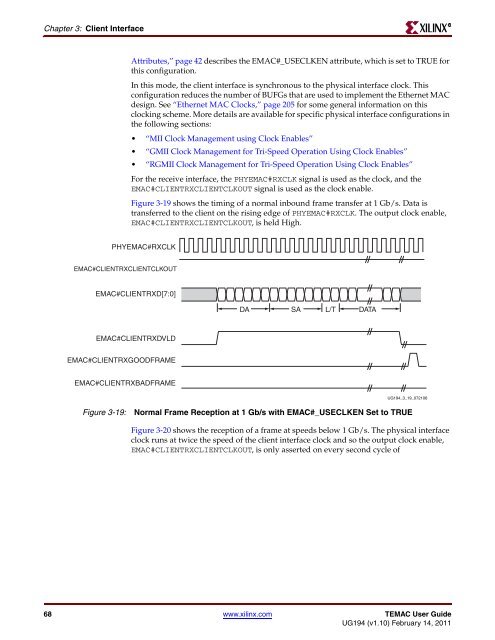

Attributes,” page 42 describes the E<strong>MAC</strong>#_USECLKEN attribute, which is set to TRUE for<br />

this configuration.<br />

In this mode, the client interface is synchronous to the physical interface clock. This<br />

configuration reduces the number of BUFGs that are used to implement the <strong>Ethernet</strong> <strong>MAC</strong><br />

design. See “<strong>Ethernet</strong> <strong>MAC</strong> Clocks,” page 205 for some general information on this<br />

clocking scheme. More details are available for specific physical interface configurations in<br />

the following sections:<br />

“MII Clock Management using Clock Enables”<br />

“GMII Clock Management for <strong>Tri</strong>-Speed Operation Using Clock Enables”<br />

“RGMII Clock Management for <strong>Tri</strong>-Speed Operation Using Clock Enables”<br />

For the receive interface, the PHYE<strong>MAC</strong>#RXCLK signal is used as the clock, and the<br />

E<strong>MAC</strong>#CLIENTRXCLIENTCLKOUT signal is used as the clock enable.<br />

Figure 3-19 shows the timing of a normal inbound frame transfer at 1 Gb/s. Data is<br />

transferred to the client on the rising edge of PHYE<strong>MAC</strong>#RXCLK. The output clock enable,<br />

E<strong>MAC</strong>#CLIENTRXCLIENTCLKOUT, is held High.<br />

PHYE<strong>MAC</strong>#RXCLK<br />

E<strong>MAC</strong>#CLIENTRXCLIENTCLKOUT<br />

E<strong>MAC</strong>#CLIENTRXD[7:0]<br />

E<strong>MAC</strong>#CLIENTRXDVLD<br />

E<strong>MAC</strong>#CLIENTRXGOODFRAME<br />

E<strong>MAC</strong>#CLIENTRXBADFRAME<br />

DA SA L/T DATA<br />

<strong>UG194</strong>_3_19_072106<br />

Figure 3-19: Normal Frame Reception at 1 Gb/s with E<strong>MAC</strong>#_USECLKEN Set to TRUE<br />

Figure 3-20 shows the reception of a frame at speeds below 1 Gb/s. The physical interface<br />

clock runs at twice the speed of the client interface clock and so the output clock enable,<br />

E<strong>MAC</strong>#CLIENTRXCLIENTCLKOUT, is only asserted on every second cycle of<br />

68 www.xilinx.com TE<strong>MAC</strong> User Guide<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

R