Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Chapter 6: Physical Interface<br />

DCM<br />

CLKFB CLK0<br />

CLKIN CLKFX<br />

Locked<br />

CLKFX_MULTIPLY = 2<br />

CLKFX_DIVIDE = 1<br />

Tx<br />

Client<br />

Logic<br />

The PLLLKDET signal from the RocketIO serial transceiver (indicating that its internal<br />

PLLs have locked) is routed to the CLIENTE<strong>MAC</strong>#DCMLOCKED input port of the <strong>Ethernet</strong><br />

<strong>MAC</strong>. This ensures that the state machines of the <strong>Ethernet</strong> <strong>MAC</strong> are held in reset until the<br />

RocketIO serial transceiver has locked and its clocks are running cleanly.<br />

As described in “<strong>Ethernet</strong> <strong>MAC</strong> Clocks,” page 205, the following clock signals are unused:<br />

E<strong>MAC</strong>#CLIENTRXCLIENTCLKOUT<br />

E<strong>MAC</strong>#CLIENTTXCLIENTCLKOUT<br />

E<strong>MAC</strong>#PHYTXGMIIMIICLKOUT<br />

PHYE<strong>MAC</strong>#TXGMIIMIICLKIN<br />

PHYE<strong>MAC</strong>#MIITXCLK<br />

PHYE<strong>MAC</strong>#RXCLK<br />

The outputs can be left unconnected, and inputs should be tied to Low.<br />

16-Bit Data Client<br />

BUFG<br />

BUFG<br />

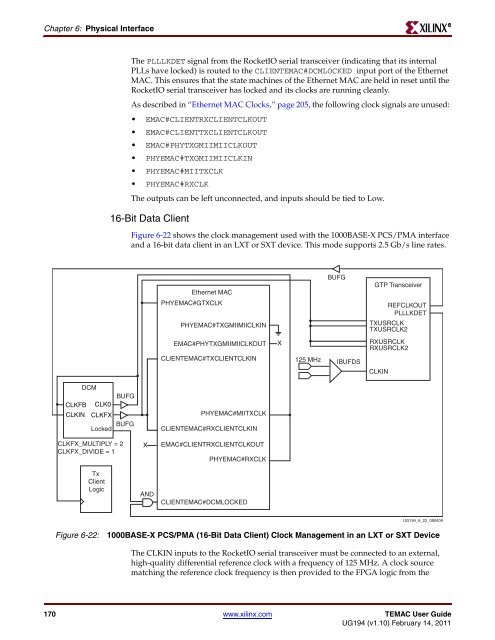

Figure 6-22 shows the clock management used with the 1000BASE-X PCS/PMA interface<br />

and a 16-bit data client in an LXT or SXT device. This mode supports 2.5 Gb/s line rates.<br />

AND<br />

X<br />

<strong>Ethernet</strong> <strong>MAC</strong><br />

PHYE<strong>MAC</strong>#GTXCLK<br />

PHYE<strong>MAC</strong>#TXGMIIMIICLKIN<br />

E<strong>MAC</strong>#PHYTXGMIIMIICLKOUT<br />

CLIENTE<strong>MAC</strong>#TXCLIENTCLKIN<br />

PHYE<strong>MAC</strong>#MIITXCLK<br />

CLIENTE<strong>MAC</strong>#RXCLIENTCLKIN<br />

E<strong>MAC</strong>#CLIENTRXCLIENTCLKOUT<br />

PHYE<strong>MAC</strong>#RXCLK<br />

CLIENTE<strong>MAC</strong>#DCMLOCKED<br />

125 MHz<br />

IBUFDS<br />

GTP Transceiver<br />

TXUSRCLK<br />

TXUSRCLK2<br />

RXUSRCLK<br />

RXUSRCLK2<br />

Figure 6-22: 1000BASE-X PCS/PMA (16-Bit Data Client) Clock Management in an LXT or SXT Device<br />

The CLKIN inputs to the RocketIO serial transceiver must be connected to an external,<br />

high-quality differential reference clock with a frequency of 125 MHz. A clock source<br />

matching the reference clock frequency is then provided to the <strong>FPGA</strong> logic from the<br />

170 www.xilinx.com TE<strong>MAC</strong> User Guide<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

X<br />

BUFG<br />

CLKIN<br />

REFCLKOUT<br />

PLLLKDET<br />

<strong>UG194</strong>_6_22_080409<br />

R