Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

R<br />

Using the DCR Bus<br />

The IRENABLE_e# register is programmed to allow updating of the interrupt request in<br />

the IRSTATUS_e# register. When an enable bit is cleared, the corresponding bit in the<br />

IRSTATUS_e# register is not updated.<br />

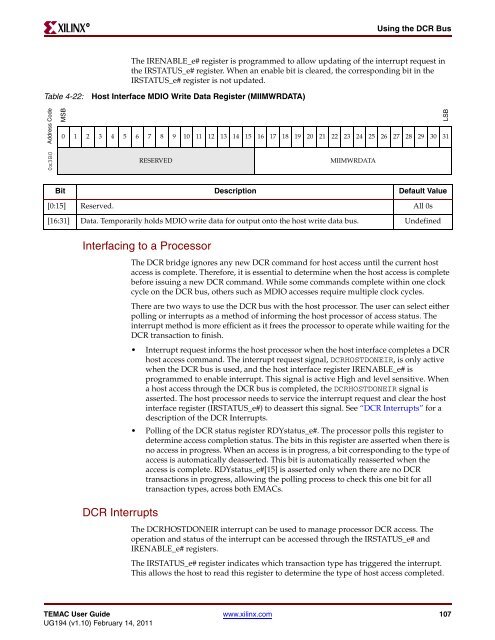

Table 4-22: Host Interface MDIO Write Data Register (MIIMWRDATA)<br />

Address Code<br />

0x3B0<br />

MSB<br />

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31<br />

Interfacing to a Processor<br />

DCR Interrupts<br />

RESERVED MIIMWRDATA<br />

Bit Description Default Value<br />

[0:15] Reserved. All 0s<br />

[16:31] Data. Temporarily holds MDIO write data for output onto the host write data bus. Undefined<br />

The DCR bridge ignores any new DCR command for host access until the current host<br />

access is complete. Therefore, it is essential to determine when the host access is complete<br />

before issuing a new DCR command. While some commands complete within one clock<br />

cycle on the DCR bus, others such as MDIO accesses require multiple clock cycles.<br />

There are two ways to use the DCR bus with the host processor. The user can select either<br />

polling or interrupts as a method of informing the host processor of access status. The<br />

interrupt method is more efficient as it frees the processor to operate while waiting for the<br />

DCR transaction to finish.<br />

Interrupt request informs the host processor when the host interface completes a DCR<br />

host access command. The interrupt request signal, DCRHOSTDONEIR, is only active<br />

when the DCR bus is used, and the host interface register IRENABLE_e# is<br />

programmed to enable interrupt. This signal is active High and level sensitive. When<br />

a host access through the DCR bus is completed, the DCRHOSTDONEIR signal is<br />

asserted. The host processor needs to service the interrupt request and clear the host<br />

interface register (IRSTATUS_e#) to deassert this signal. See “DCR Interrupts” for a<br />

description of the DCR Interrupts.<br />

Polling of the DCR status register RDYstatus_e#. The processor polls this register to<br />

determine access completion status. The bits in this register are asserted when there is<br />

no access in progress. When an access is in progress, a bit corresponding to the type of<br />

access is automatically deasserted. This bit is automatically reasserted when the<br />

access is complete. RDYstatus_e#[15] is asserted only when there are no DCR<br />

transactions in progress, allowing the polling process to check this one bit for all<br />

transaction types, across both E<strong>MAC</strong>s.<br />

The DCRHOSTDONEIR interrupt can be used to manage processor DCR access. The<br />

operation and status of the interrupt can be accessed through the IRSTATUS_e# and<br />

IRENABLE_e# registers.<br />

The IRSTATUS_e# register indicates which transaction type has triggered the interrupt.<br />

This allows the host to read this register to determine the type of host access completed.<br />

TE<strong>MAC</strong> User Guide www.xilinx.com 107<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

LSB