Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Chapter 2: <strong>Ethernet</strong> <strong>MAC</strong> Overview<br />

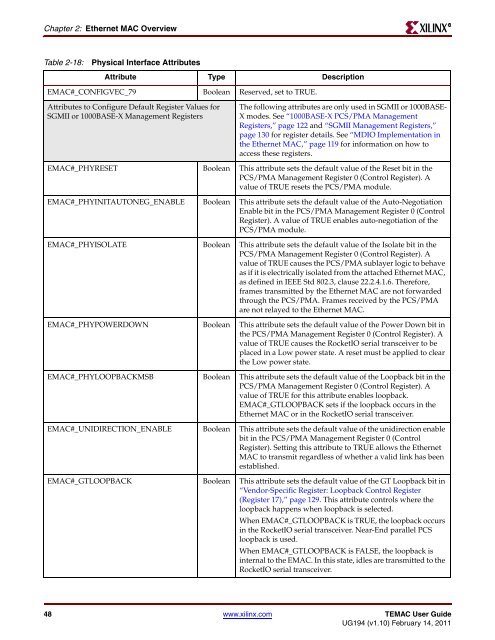

Table 2-18: Physical Interface Attributes<br />

Attribute Type Description<br />

E<strong>MAC</strong>#_CONFIGVEC_79 Boolean Reserved, set to TRUE.<br />

Attributes to Configure Default Register Values for<br />

SGMII or 1000BASE-X Management Registers<br />

The following attributes are only used in SGMII or 1000BASE-<br />

X modes. See “1000BASE-X PCS/PMA Management<br />

Registers,” page 122 and “SGMII Management Registers,”<br />

page 130 for register details. See “MDIO Implementation in<br />

the <strong>Ethernet</strong> <strong>MAC</strong>,” page 119 for information on how to<br />

access these registers.<br />

E<strong>MAC</strong>#_PHYRESET Boolean This attribute sets the default value of the Reset bit in the<br />

PCS/PMA Management Register 0 (Control Register). A<br />

value of TRUE resets the PCS/PMA module.<br />

E<strong>MAC</strong>#_PHYINITAUTONEG_ENABLE Boolean This attribute sets the default value of the Auto-Negotiation<br />

Enable bit in the PCS/PMA Management Register 0 (Control<br />

Register). A value of TRUE enables auto-negotiation of the<br />

PCS/PMA module.<br />

E<strong>MAC</strong>#_PHYISOLATE Boolean This attribute sets the default value of the Isolate bit in the<br />

PCS/PMA Management Register 0 (Control Register). A<br />

value of TRUE causes the PCS/PMA sublayer logic to behave<br />

as if it is electrically isolated from the attached <strong>Ethernet</strong> <strong>MAC</strong>,<br />

as defined in IEEE Std 802.3, clause 22.2.4.1.6. Therefore,<br />

frames transmitted by the <strong>Ethernet</strong> <strong>MAC</strong> are not forwarded<br />

through the PCS/PMA. Frames received by the PCS/PMA<br />

are not relayed to the <strong>Ethernet</strong> <strong>MAC</strong>.<br />

E<strong>MAC</strong>#_PHYPOWERDOWN Boolean This attribute sets the default value of the Power Down bit in<br />

the PCS/PMA Management Register 0 (Control Register). A<br />

value of TRUE causes the RocketIO serial transceiver to be<br />

placed in a Low power state. A reset must be applied to clear<br />

the Low power state.<br />

E<strong>MAC</strong>#_PHYLOOPBACKMSB Boolean This attribute sets the default value of the Loopback bit in the<br />

PCS/PMA Management Register 0 (Control Register). A<br />

value of TRUE for this attribute enables loopback.<br />

E<strong>MAC</strong>#_GTLOOPBACK sets if the loopback occurs in the<br />

<strong>Ethernet</strong> <strong>MAC</strong> or in the RocketIO serial transceiver.<br />

E<strong>MAC</strong>#_UNIDIRECTION_ENABLE Boolean This attribute sets the default value of the unidirection enable<br />

bit in the PCS/PMA Management Register 0 (Control<br />

Register). Setting this attribute to TRUE allows the <strong>Ethernet</strong><br />

<strong>MAC</strong> to transmit regardless of whether a valid link has been<br />

established.<br />

E<strong>MAC</strong>#_GTLOOPBACK Boolean This attribute sets the default value of the GT Loopback bit in<br />

“Vendor-Specific Register: Loopback Control Register<br />

(Register 17),” page 129. This attribute controls where the<br />

loopback happens when loopback is selected.<br />

When E<strong>MAC</strong>#_GTLOOPBACK is TRUE, the loopback occurs<br />

in the RocketIO serial transceiver. Near-End parallel PCS<br />

loopback is used.<br />

When E<strong>MAC</strong>#_GTLOOPBACK is FALSE, the loopback is<br />

internal to the E<strong>MAC</strong>. In this state, idles are transmitted to the<br />

RocketIO serial transceiver.<br />

48 www.xilinx.com TE<strong>MAC</strong> User Guide<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

R