Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Chapter 3: Client Interface<br />

Statistics Vectors<br />

Transmitter Statistics Vector<br />

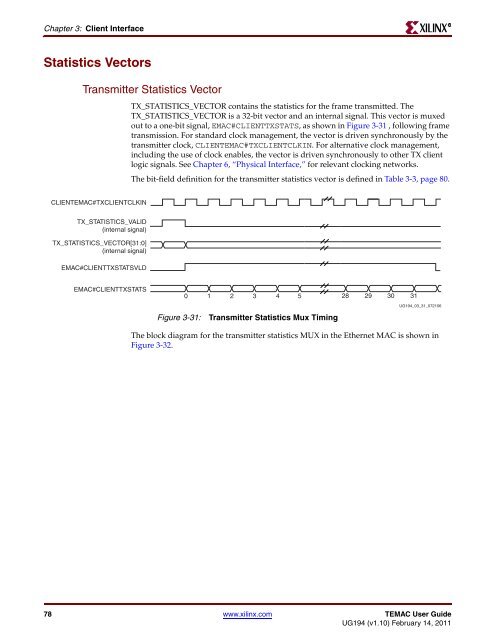

CLIENTE<strong>MAC</strong>#TXCLIENTCLKIN<br />

TX_STATISTICS_VALID<br />

(internal signal)<br />

TX_STATISTICS_VECTOR[31:0]<br />

(internal signal)<br />

E<strong>MAC</strong>#CLIENTTXSTATSVLD<br />

E<strong>MAC</strong>#CLIENTTXSTATS<br />

TX_STATISTICS_VECTOR contains the statistics for the frame transmitted. The<br />

TX_STATISTICS_VECTOR is a 32-bit vector and an internal signal. This vector is muxed<br />

out to a one-bit signal, E<strong>MAC</strong>#CLIENTTXSTATS, as shown in Figure 3-31 , following frame<br />

transmission. For standard clock management, the vector is driven synchronously by the<br />

transmitter clock, CLIENTE<strong>MAC</strong>#TXCLIENTCLKIN. For alternative clock management,<br />

including the use of clock enables, the vector is driven synchronously to other TX client<br />

logic signals. See Chapter 6, “Physical Interface,” for relevant clocking networks.<br />

The bit-field definition for the transmitter statistics vector is defined in Table 3-3, page 80.<br />

0 1 2 3 4 5 28 29 30 31<br />

Figure 3-31: Transmitter Statistics Mux Timing<br />

<strong>UG194</strong>_03_31_072106<br />

The block diagram for the transmitter statistics MUX in the <strong>Ethernet</strong> <strong>MAC</strong> is shown in<br />

Figure 3-32.<br />

78 www.xilinx.com TE<strong>MAC</strong> User Guide<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

R