Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Chapter 4: Host/DCR Bus Interfaces<br />

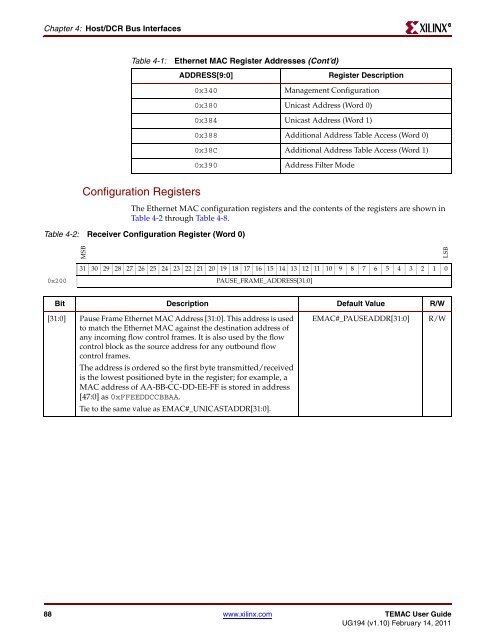

Table 4-1: <strong>Ethernet</strong> <strong>MAC</strong> Register Addresses (Cont’d)<br />

Configuration Registers<br />

ADDRESS[9:0] Register Description<br />

0x340 Management Configuration<br />

0x380 Unicast Address (Word 0)<br />

0x384 Unicast Address (Word 1)<br />

0x388 Additional Address Table Access (Word 0)<br />

0x38C Additional Address Table Access (Word 1)<br />

0x390 Address Filter <strong>Mode</strong><br />

The <strong>Ethernet</strong> <strong>MAC</strong> configuration registers and the contents of the registers are shown in<br />

Table 4-2 through Table 4-8.<br />

Table 4-2: Receiver Configuration Register (Word 0)<br />

MSB<br />

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0<br />

0x200 PAUSE_FRAME_ADDRESS[31:0]<br />

Bit Description Default Value R/W<br />

[31:0] Pause Frame <strong>Ethernet</strong> <strong>MAC</strong> Address [31:0]. This address is used<br />

to match the <strong>Ethernet</strong> <strong>MAC</strong> against the destination address of<br />

any incoming flow control frames. It is also used by the flow<br />

control block as the source address for any outbound flow<br />

control frames.<br />

The address is ordered so the first byte transmitted/received<br />

is the lowest positioned byte in the register; for example, a<br />

<strong>MAC</strong> address of AA-BB-CC-DD-EE-FF is stored in address<br />

[47:0] as 0xFFEEDDCCBBAA.<br />

Tie to the same value as E<strong>MAC</strong>#_UNICASTADDR[31:0].<br />

88 www.xilinx.com TE<strong>MAC</strong> User Guide<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

LSB<br />

E<strong>MAC</strong>#_PAUSEADDR[31:0] R/W<br />

R