Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

R<br />

MDIO Implementation in the <strong>Ethernet</strong> <strong>MAC</strong><br />

Generic<br />

Host Bus<br />

DCR Bus<br />

Host<br />

Interface<br />

DCR Bridge<br />

MDIO Implementation in the <strong>Ethernet</strong> <strong>MAC</strong><br />

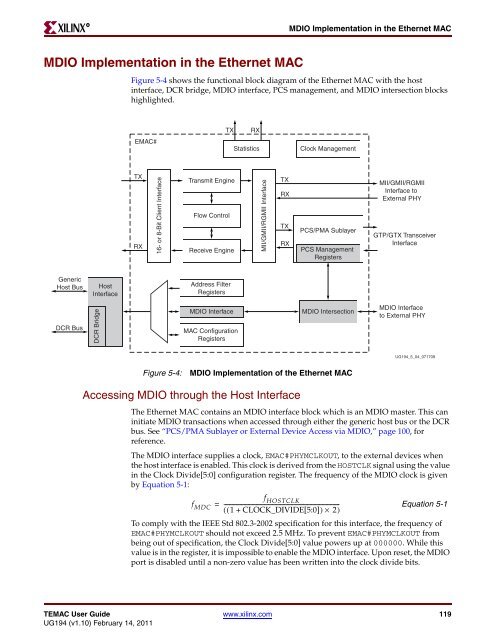

Figure 5-4 shows the functional block diagram of the <strong>Ethernet</strong> <strong>MAC</strong> with the host<br />

interface, DCR bridge, MDIO interface, PCS management, and MDIO intersection blocks<br />

highlighted.<br />

E<strong>MAC</strong>#<br />

TX<br />

RX<br />

16- or 8-Bit Client Interface<br />

Transmit Engine<br />

Flow Control<br />

Receive Engine<br />

Address Filter<br />

Registers<br />

MDIO Interface<br />

<strong>MAC</strong> Configuration<br />

Registers<br />

TX RX<br />

Statistics<br />

Figure 5-4: MDIO Implementation of the <strong>Ethernet</strong> <strong>MAC</strong><br />

Accessing MDIO through the Host Interface<br />

Clock Management<br />

MII/GMII/RGMII<br />

Interface to<br />

External PHY<br />

GTP/GTX Transceiver<br />

Interface<br />

MDIO Interface<br />

to External PHY<br />

<strong>UG194</strong>_5_04_071709<br />

The <strong>Ethernet</strong> <strong>MAC</strong> contains an MDIO interface block which is an MDIO master. This can<br />

initiate MDIO transactions when accessed through either the generic host bus or the DCR<br />

bus. See “PCS/PMA Sublayer or External Device Access via MDIO,” page 100, for<br />

reference.<br />

The MDIO interface supplies a clock, E<strong>MAC</strong>#PHYMCLKOUT, to the external devices when<br />

the host interface is enabled. This clock is derived from the HOSTCLK signal using the value<br />

in the Clock Divide[5:0] configuration register. The frequency of the MDIO clock is given<br />

by Equation 5-1:<br />

fHOSTCLK fMDC =<br />

-------------------------------------------------------------------------------------<br />

Equation 5-1<br />

( ( 1 + CLOCK_DIVIDE[5:0] ) × 2)<br />

To comply with the IEEE Std 802.3-2002 specification for this interface, the frequency of<br />

E<strong>MAC</strong>#PHYMCLKOUT should not exceed 2.5 MHz. To prevent E<strong>MAC</strong>#PHYMCLKOUT from<br />

being out of specification, the Clock Divide[5:0] value powers up at 000000. While this<br />

value is in the register, it is impossible to enable the MDIO interface. Upon reset, the MDIO<br />

port is disabled until a non-zero value has been written into the clock divide bits.<br />

TE<strong>MAC</strong> User Guide www.xilinx.com 119<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

MII/GMII/RGMII Interface<br />

TX<br />

RX<br />

TX<br />

RX<br />

PCS/PMA Sublayer<br />

PCS Management<br />

Registers<br />

MDIO Intersection