Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Chapter 6: Physical Interface<br />

Media Independent Interface (MII)<br />

The Media Independent Interface (MII), defined in IEEE 802.3, clause 22, is a parallel<br />

interface that connects a 10-Mb/s and/or 100-Mb/s capable <strong>MAC</strong> to the physical<br />

sublayers.<br />

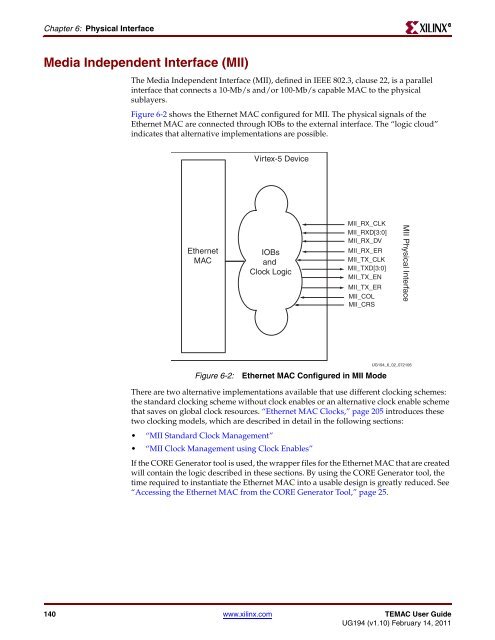

Figure 6-2 shows the <strong>Ethernet</strong> <strong>MAC</strong> configured for MII. The physical signals of the<br />

<strong>Ethernet</strong> <strong>MAC</strong> are connected through IOBs to the external interface. The “logic cloud”<br />

indicates that alternative implementations are possible.<br />

<strong>Ethernet</strong><br />

<strong>MAC</strong><br />

Figure 6-2: <strong>Ethernet</strong> <strong>MAC</strong> Configured in MII <strong>Mode</strong><br />

There are two alternative implementations available that use different clocking schemes:<br />

the standard clocking scheme without clock enables or an alternative clock enable scheme<br />

that saves on global clock resources. “<strong>Ethernet</strong> <strong>MAC</strong> Clocks,” page 205 introduces these<br />

two clocking models, which are described in detail in the following sections:<br />

“MII Standard Clock Management”<br />

<strong>Virtex</strong>-5 Device<br />

IOBs<br />

and<br />

Clock Logic<br />

MII_RX_CLK<br />

MII_RXD[3:0]<br />

MII_RX_DV<br />

MII_RX_ER<br />

MII_TX_CLK<br />

MII_TXD[3:0]<br />

MII_TX_EN<br />

MII_TX_ER<br />

MII_COL<br />

MII_CRS<br />

“MII Clock Management using Clock Enables”<br />

If the CORE Generator tool is used, the wrapper files for the <strong>Ethernet</strong> <strong>MAC</strong> that are created<br />

will contain the logic described in these sections. By using the CORE Generator tool, the<br />

time required to instantiate the <strong>Ethernet</strong> <strong>MAC</strong> into a usable design is greatly reduced. See<br />

“Accessing the <strong>Ethernet</strong> <strong>MAC</strong> from the CORE Generator Tool,” page 25.<br />

140 www.xilinx.com TE<strong>MAC</strong> User Guide<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

MII Physical Interface<br />

<strong>UG194</strong>_6_02_072106<br />

R