Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

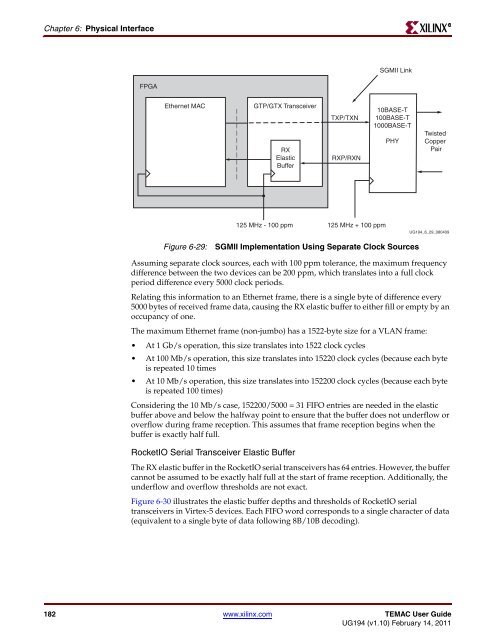

Chapter 6: Physical Interface<br />

<strong>FPGA</strong><br />

<strong>Ethernet</strong> <strong>MAC</strong> GTP/GTX Transceiver<br />

RX<br />

Elastic<br />

Buffer<br />

125 MHz - 100 ppm<br />

Figure 6-29: SGMII Implementation Using Separate Clock Sources<br />

Assuming separate clock sources, each with 100 ppm tolerance, the maximum frequency<br />

difference between the two devices can be 200 ppm, which translates into a full clock<br />

period difference every 5000 clock periods.<br />

Relating this information to an <strong>Ethernet</strong> frame, there is a single byte of difference every<br />

5000 bytes of received frame data, causing the RX elastic buffer to either fill or empty by an<br />

occupancy of one.<br />

The maximum <strong>Ethernet</strong> frame (non-jumbo) has a 1522-byte size for a VLAN frame:<br />

At 1 Gb/s operation, this size translates into 1522 clock cycles<br />

At 100 Mb/s operation, this size translates into 15220 clock cycles (because each byte<br />

is repeated 10 times<br />

At 10 Mb/s operation, this size translates into 152200 clock cycles (because each byte<br />

is repeated 100 times)<br />

Considering the 10 Mb/s case, 152200/5000 = 31 FIFO entries are needed in the elastic<br />

buffer above and below the halfway point to ensure that the buffer does not underflow or<br />

overflow during frame reception. This assumes that frame reception begins when the<br />

buffer is exactly half full.<br />

RocketIO Serial Transceiver Elastic Buffer<br />

TXP/TXN<br />

RXP/RXN<br />

125 MHz + 100 ppm<br />

SGMII Link<br />

10BASE-T<br />

100BASE-T<br />

1000BASE-T<br />

Twisted<br />

Copper<br />

Pair<br />

The RX elastic buffer in the RocketIO serial transceivers has 64 entries. However, the buffer<br />

cannot be assumed to be exactly half full at the start of frame reception. Additionally, the<br />

underflow and overflow thresholds are not exact.<br />

Figure 6-30 illustrates the elastic buffer depths and thresholds of RocketIO serial<br />

transceivers in <strong>Virtex</strong>-5 devices. Each FIFO word corresponds to a single character of data<br />

(equivalent to a single byte of data following 8B/10B decoding).<br />

182 www.xilinx.com TE<strong>MAC</strong> User Guide<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

PHY<br />

<strong>UG194</strong>_6_29_080409<br />

R