Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>FPGA</strong><br />

R<br />

Introduction to the SGMII Implementation<br />

PCS/PMA Sublayer<br />

Serial Gigabit Media Independent Interface (SGMII)<br />

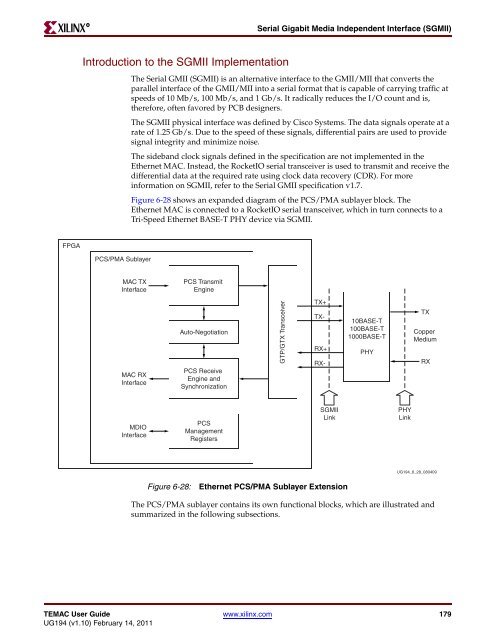

The Serial GMII (SGMII) is an alternative interface to the GMII/MII that converts the<br />

parallel interface of the GMII/MII into a serial format that is capable of carrying traffic at<br />

speeds of 10 Mb/s, 100 Mb/s, and 1 Gb/s. It radically reduces the I/O count and is,<br />

therefore, often favored by PCB designers.<br />

The SGMII physical interface was defined by Cisco Systems. The data signals operate at a<br />

rate of 1.25 Gb/s. Due to the speed of these signals, differential pairs are used to provide<br />

signal integrity and minimize noise.<br />

The sideband clock signals defined in the specification are not implemented in the<br />

<strong>Ethernet</strong> <strong>MAC</strong>. Instead, the RocketIO serial transceiver is used to transmit and receive the<br />

differential data at the required rate using clock data recovery (CDR). For more<br />

information on SGMII, refer to the Serial GMII specification v1.7.<br />

Figure 6-28 shows an expanded diagram of the PCS/PMA sublayer block. The<br />

<strong>Ethernet</strong> <strong>MAC</strong> is connected to a RocketIO serial transceiver, which in turn connects to a<br />

<strong>Tri</strong>-Speed <strong>Ethernet</strong> BASE-T PHY device via SGMII.<br />

<strong>MAC</strong> TX<br />

Interface<br />

<strong>MAC</strong> RX<br />

Interface<br />

MDIO<br />

Interface<br />

PCS Transmit<br />

Engine<br />

Auto-Negotiation<br />

PCS Receive<br />

Engine and<br />

Synchronization<br />

PCS<br />

Management<br />

Registers<br />

Figure 6-28: <strong>Ethernet</strong> PCS/PMA Sublayer Extension<br />

<strong>UG194</strong>_6_28_080409<br />

The PCS/PMA sublayer contains its own functional blocks, which are illustrated and<br />

summarized in the following subsections.<br />

TE<strong>MAC</strong> User Guide www.xilinx.com 179<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

GTP/GTX Transceiver<br />

TX+<br />

TX-<br />

RX+<br />

RX-<br />

SGMII<br />

Link<br />

10BASE-T<br />

100BASE-T<br />

1000BASE-T<br />

PHY<br />

PHY<br />

Link<br />

TX<br />

Copper<br />

Medium<br />

RX