Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Chapter 2: <strong>Ethernet</strong> <strong>MAC</strong> Overview<br />

On the physical side of the <strong>Ethernet</strong> <strong>MAC</strong>, a common MII/GMII/RGMII interface block is<br />

shown. When the physical interface of the <strong>Ethernet</strong> <strong>MAC</strong> is configured to MII/GMII or<br />

RGMII, these signals can be used via standard I/Os to connect to an external physical<br />

interface. When the physical interface is configured in 1000BASE-X or SGMII mode, the<br />

PCS/PMA sublayer block in the <strong>Ethernet</strong> <strong>MAC</strong> is enabled. The PCS/PMA sublayer block<br />

interfaces directly to the RocketIO serial transceiver. See “Physical Interface,” page 137<br />

for information on all physical interfaces, including clocking schemes and interfacing with<br />

serial transceivers.<br />

The clock management module automatically configures the output clocks to the correct<br />

frequency based on the internal speed of the <strong>Ethernet</strong> <strong>MAC</strong> (10 Mb/s, 100 Mb/s, or<br />

1000 Mb/s) and the <strong>Ethernet</strong> <strong>MAC</strong> mode settings (GMII, MII, RGMII, SGMII, and<br />

1000BASE-X).<br />

<strong>Ethernet</strong> <strong>MAC</strong> Configuration Options<br />

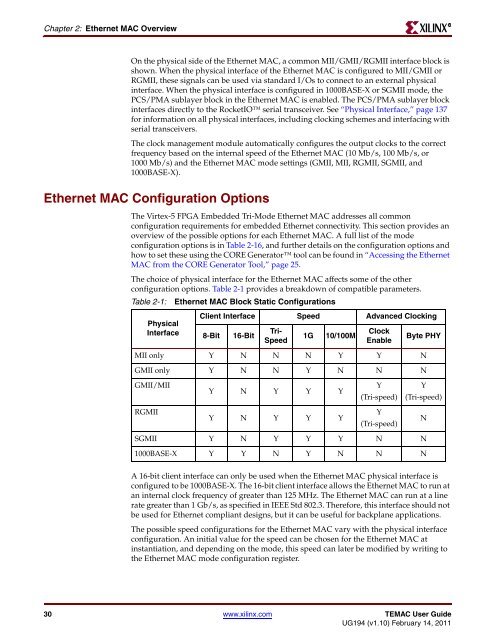

The <strong>Virtex</strong>-5 <strong>FPGA</strong> <strong>Embedded</strong> <strong>Tri</strong>-<strong>Mode</strong> <strong>Ethernet</strong> <strong>MAC</strong> addresses all common<br />

configuration requirements for embedded <strong>Ethernet</strong> connectivity. This section provides an<br />

overview of the possible options for each <strong>Ethernet</strong> <strong>MAC</strong>. A full list of the mode<br />

configuration options is in Table 2-16, and further details on the configuration options and<br />

how to set these using the CORE Generator tool can be found in “Accessing the <strong>Ethernet</strong><br />

<strong>MAC</strong> from the CORE Generator Tool,” page 25.<br />

The choice of physical interface for the <strong>Ethernet</strong> <strong>MAC</strong> affects some of the other<br />

configuration options. Table 2-1 provides a breakdown of compatible parameters.<br />

Table 2-1: <strong>Ethernet</strong> <strong>MAC</strong> Block Static Configurations<br />

Physical<br />

Interface<br />

Client Interface Speed Advanced Clocking<br />

8-Bit 16-Bit<br />

<strong>Tri</strong>-<br />

Speed<br />

1G 10/100M<br />

Clock<br />

Enable<br />

Byte PHY<br />

MII only Y N N N Y Y N<br />

GMII only Y N N Y N N N<br />

GMII/MII<br />

Y N Y Y Y<br />

Y<br />

(<strong>Tri</strong>-speed)<br />

Y<br />

(<strong>Tri</strong>-speed)<br />

RGMII<br />

Y N Y Y Y<br />

Y<br />

(<strong>Tri</strong>-speed)<br />

N<br />

SGMII Y N Y Y Y N N<br />

1000BASE-X Y Y N Y N N N<br />

A 16-bit client interface can only be used when the <strong>Ethernet</strong> <strong>MAC</strong> physical interface is<br />

configured to be 1000BASE-X. The 16-bit client interface allows the <strong>Ethernet</strong> <strong>MAC</strong> to run at<br />

an internal clock frequency of greater than 125 MHz. The <strong>Ethernet</strong> <strong>MAC</strong> can run at a line<br />

rate greater than 1 Gb/s, as specified in IEEE Std 802.3. Therefore, this interface should not<br />

be used for <strong>Ethernet</strong> compliant designs, but it can be useful for backplane applications.<br />

The possible speed configurations for the <strong>Ethernet</strong> <strong>MAC</strong> vary with the physical interface<br />

configuration. An initial value for the speed can be chosen for the <strong>Ethernet</strong> <strong>MAC</strong> at<br />

instantiation, and depending on the mode, this speed can later be modified by writing to<br />

the <strong>Ethernet</strong> <strong>MAC</strong> mode configuration register.<br />

30 www.xilinx.com TE<strong>MAC</strong> User Guide<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

R