Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Chapter 2: <strong>Ethernet</strong> <strong>MAC</strong> Overview<br />

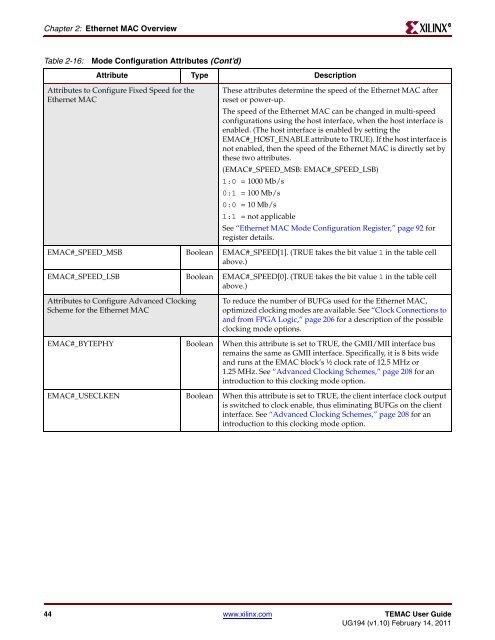

Table 2-16: <strong>Mode</strong> Configuration Attributes (Cont’d)<br />

Attribute Type Description<br />

Attributes to Configure Fixed Speed for the<br />

<strong>Ethernet</strong> <strong>MAC</strong><br />

These attributes determine the speed of the <strong>Ethernet</strong> <strong>MAC</strong> after<br />

reset or power-up.<br />

The speed of the <strong>Ethernet</strong> <strong>MAC</strong> can be changed in multi-speed<br />

configurations using the host interface, when the host interface is<br />

enabled. (The host interface is enabled by setting the<br />

E<strong>MAC</strong>#_HOST_ENABLE attribute to TRUE). If the host interface is<br />

not enabled, then the speed of the <strong>Ethernet</strong> <strong>MAC</strong> is directly set by<br />

these two attributes.<br />

(E<strong>MAC</strong>#_SPEED_MSB: E<strong>MAC</strong>#_SPEED_LSB)<br />

1:0 = 1000 Mb/s<br />

0:1 = 100 Mb/s<br />

0:0 = 10 Mb/s<br />

1:1 = not applicable<br />

See “<strong>Ethernet</strong> <strong>MAC</strong> <strong>Mode</strong> Configuration Register,” page 92 for<br />

register details.<br />

E<strong>MAC</strong>#_SPEED_MSB Boolean E<strong>MAC</strong>#_SPEED[1]. (TRUE takes the bit value 1 in the table cell<br />

above.)<br />

E<strong>MAC</strong>#_SPEED_LSB Boolean E<strong>MAC</strong>#_SPEED[0]. (TRUE takes the bit value 1 in the table cell<br />

above.)<br />

Attributes to Configure Advanced Clocking<br />

Scheme for the <strong>Ethernet</strong> <strong>MAC</strong><br />

To reduce the number of BUFGs used for the <strong>Ethernet</strong> <strong>MAC</strong>,<br />

optimized clocking modes are available. See “Clock Connections to<br />

and from <strong>FPGA</strong> Logic,” page 206 for a description of the possible<br />

clocking mode options.<br />

E<strong>MAC</strong>#_BYTEPHY Boolean When this attribute is set to TRUE, the GMII/MII interface bus<br />

remains the same as GMII interface. Specifically, it is 8 bits wide<br />

and runs at the E<strong>MAC</strong> block’s ½ clock rate of 12.5 MHz or<br />

1.25 MHz. See “Advanced Clocking Schemes,” page 208 for an<br />

introduction to this clocking mode option.<br />

E<strong>MAC</strong>#_USECLKEN Boolean When this attribute is set to TRUE, the client interface clock output<br />

is switched to clock enable, thus eliminating BUFGs on the client<br />

interface. See “Advanced Clocking Schemes,” page 208 for an<br />

introduction to this clocking mode option.<br />

44 www.xilinx.com TE<strong>MAC</strong> User Guide<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

R