Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

R<br />

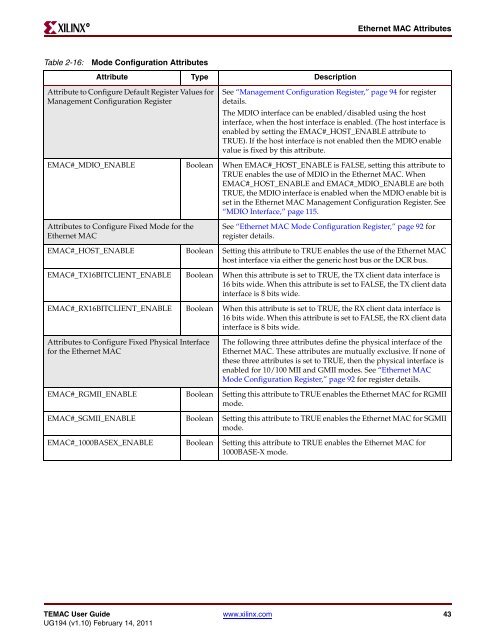

Table 2-16: <strong>Mode</strong> Configuration Attributes<br />

Attribute Type Description<br />

Attribute to Configure Default Register Values for<br />

Management Configuration Register<br />

<strong>Ethernet</strong> <strong>MAC</strong> Attributes<br />

See “Management Configuration Register,” page 94 for register<br />

details.<br />

The MDIO interface can be enabled/disabled using the host<br />

interface, when the host interface is enabled. (The host interface is<br />

enabled by setting the E<strong>MAC</strong>#_HOST_ENABLE attribute to<br />

TRUE). If the host interface is not enabled then the MDIO enable<br />

value is fixed by this attribute.<br />

E<strong>MAC</strong>#_MDIO_ENABLE Boolean When E<strong>MAC</strong>#_HOST_ENABLE is FALSE, setting this attribute to<br />

TRUE enables the use of MDIO in the <strong>Ethernet</strong> <strong>MAC</strong>. When<br />

E<strong>MAC</strong>#_HOST_ENABLE and E<strong>MAC</strong>#_MDIO_ENABLE are both<br />

TRUE, the MDIO interface is enabled when the MDIO enable bit is<br />

set in the <strong>Ethernet</strong> <strong>MAC</strong> Management Configuration Register. See<br />

“MDIO Interface,” page 115.<br />

Attributes to Configure Fixed <strong>Mode</strong> for the<br />

<strong>Ethernet</strong> <strong>MAC</strong><br />

See “<strong>Ethernet</strong> <strong>MAC</strong> <strong>Mode</strong> Configuration Register,” page 92 for<br />

register details.<br />

E<strong>MAC</strong>#_HOST_ENABLE Boolean Setting this attribute to TRUE enables the use of the <strong>Ethernet</strong> <strong>MAC</strong><br />

host interface via either the generic host bus or the DCR bus.<br />

E<strong>MAC</strong>#_TX16BITCLIENT_ENABLE Boolean When this attribute is set to TRUE, the TX client data interface is<br />

16 bits wide. When this attribute is set to FALSE, the TX client data<br />

interface is 8 bits wide.<br />

E<strong>MAC</strong>#_RX16BITCLIENT_ENABLE Boolean When this attribute is set to TRUE, the RX client data interface is<br />

16 bits wide. When this attribute is set to FALSE, the RX client data<br />

interface is 8 bits wide.<br />

Attributes to Configure Fixed Physical Interface<br />

for the <strong>Ethernet</strong> <strong>MAC</strong><br />

The following three attributes define the physical interface of the<br />

<strong>Ethernet</strong> <strong>MAC</strong>. These attributes are mutually exclusive. If none of<br />

these three attributes is set to TRUE, then the physical interface is<br />

enabled for 10/100 MII and GMII modes. See “<strong>Ethernet</strong> <strong>MAC</strong><br />

<strong>Mode</strong> Configuration Register,” page 92 for register details.<br />

E<strong>MAC</strong>#_RGMII_ENABLE Boolean Setting this attribute to TRUE enables the <strong>Ethernet</strong> <strong>MAC</strong> for RGMII<br />

mode.<br />

E<strong>MAC</strong>#_SGMII_ENABLE Boolean Setting this attribute to TRUE enables the <strong>Ethernet</strong> <strong>MAC</strong> for SGMII<br />

mode.<br />

E<strong>MAC</strong>#_1000BASEX_ENABLE Boolean Setting this attribute to TRUE enables the <strong>Ethernet</strong> <strong>MAC</strong> for<br />

1000BASE-X mode.<br />

TE<strong>MAC</strong> User Guide www.xilinx.com 43<br />

<strong>UG194</strong> (v1.10) February 14, 2011