Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

R<br />

Number<br />

of Bytes<br />

Physical Sublayers PCS, PMA, and PMD<br />

<strong>Ethernet</strong> Protocol Overview<br />

The combination of the Physical Coding Sublayer (PCS), the Physical Medium Attachment<br />

(PMA), and the Physical Medium Dependent (PMD) sublayer constitute the physical<br />

layers for the protocol. Two main physical standards are specified:<br />

<strong>Ethernet</strong> Data Format<br />

Number<br />

of Bytes<br />

Preamble<br />

Preamble<br />

BASE-T PHYs provide a link between the <strong>MAC</strong> and copper mediums. This<br />

functionality is not offered within the <strong>Virtex</strong>-5 <strong>FPGA</strong> <strong>Embedded</strong> <strong>Tri</strong>-<strong>Mode</strong> <strong>Ethernet</strong><br />

<strong>MAC</strong>. However, external BASE-T PHY devices are readily available on the market.<br />

These can connect to the <strong>Ethernet</strong> <strong>MAC</strong>, using GMII/MII, RGMII, or SGMII<br />

interfaces.<br />

BASE-X PHYs provide a link between the <strong>MAC</strong> and (usually) fibre optic mediums.<br />

The <strong>Virtex</strong>-5 <strong>FPGA</strong> <strong>Embedded</strong> <strong>Tri</strong>-<strong>Mode</strong> <strong>Ethernet</strong> <strong>MAC</strong> is capable of supporting the<br />

1 Gb/s BASE-X standard; 1000BASE-X PCS and PMA sublayers can be offered by<br />

connecting the <strong>Ethernet</strong> <strong>MAC</strong> to a RocketIO serial transceiver. An optical transceiver<br />

can be directly connected to the RocketIO serial transceiver to complete the PMD<br />

sublayer functionality.<br />

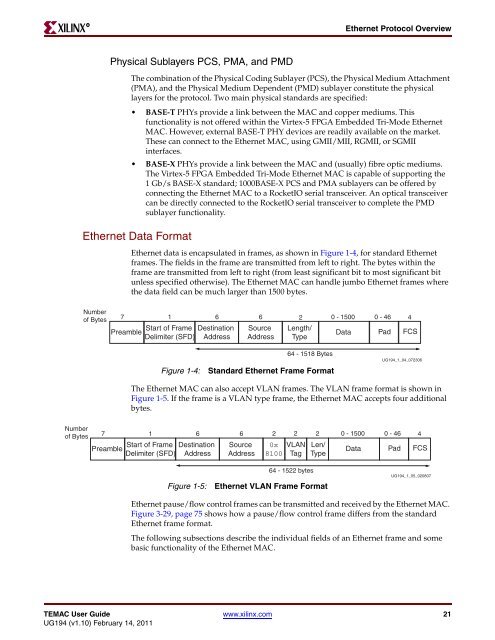

<strong>Ethernet</strong> data is encapsulated in frames, as shown in Figure 1-4, for standard <strong>Ethernet</strong><br />

frames. The fields in the frame are transmitted from left to right. The bytes within the<br />

frame are transmitted from left to right (from least significant bit to most significant bit<br />

unless specified otherwise). The <strong>Ethernet</strong> <strong>MAC</strong> can handle jumbo <strong>Ethernet</strong> frames where<br />

the data field can be much larger than 1500 bytes.<br />

7 1 6 6 2 0 - 1500 0 - 46 4<br />

Start of Frame Destination<br />

Delimiter (SFD) Address<br />

Source<br />

Address<br />

Length/<br />

Type<br />

64 - 1518 Bytes<br />

Figure 1-4: Standard <strong>Ethernet</strong> Frame Format<br />

Data Pad<br />

<strong>UG194</strong>_1_04_072306<br />

The <strong>Ethernet</strong> <strong>MAC</strong> can also accept VLAN frames. The VLAN frame format is shown in<br />

Figure 1-5. If the frame is a VLAN type frame, the <strong>Ethernet</strong> <strong>MAC</strong> accepts four additional<br />

bytes.<br />

7 1 6 6 2 2 2 0 - 1500 0 - 46 4<br />

Start of Frame Destination<br />

Delimiter (SFD) Address<br />

Source<br />

Address<br />

0x<br />

8100<br />

VLAN<br />

Tag<br />

Len/<br />

Type<br />

Data Pad FCS<br />

64 - 1522 bytes<br />

Figure 1-5: <strong>Ethernet</strong> VLAN Frame Format<br />

<strong>Ethernet</strong> pause/flow control frames can be transmitted and received by the <strong>Ethernet</strong> <strong>MAC</strong>.<br />

Figure 3-29, page 75 shows how a pause/flow control frame differs from the standard<br />

<strong>Ethernet</strong> frame format.<br />

The following subsections describe the individual fields of an <strong>Ethernet</strong> frame and some<br />

basic functionality of the <strong>Ethernet</strong> <strong>MAC</strong>.<br />

TE<strong>MAC</strong> User Guide www.xilinx.com 21<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

FCS<br />

<strong>UG194</strong>_1_05_020807