Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Chapter 3: Client Interface<br />

As shown in Figure 3-12, CLIENTE<strong>MAC</strong>#TXDVLDMSW denotes an odd number of bytes in the<br />

frame. In the odd byte case, CLIENTE<strong>MAC</strong>#TXDVLDMSW is deasserted one clock cycle earlier<br />

than the CLIENTE<strong>MAC</strong>#TXDVLD signal, after the transmission of the frame. Otherwise, these<br />

data valid signals are the same as shown in the even byte case (Figure 3-11).<br />

Back-to-Back Transfers<br />

CLIENTE<strong>MAC</strong>#TXCLIENTCLKIN<br />

PHYE<strong>MAC</strong>#MIITXCLK<br />

(CLIENTE<strong>MAC</strong>#TXCLIENTCLKIN/2)<br />

CLIENTE<strong>MAC</strong>#TXD[15:0]<br />

CLIENTE<strong>MAC</strong>#TXDVLD<br />

CLIENTE<strong>MAC</strong>#TXDVLDMSW<br />

E<strong>MAC</strong>#CLIENTTXACK<br />

CLIENTE<strong>MAC</strong>#TXUNDERRUN<br />

E<strong>MAC</strong>#CLIENTTXCOLLISION<br />

E<strong>MAC</strong>#CLIENTTXRETRANSMIT<br />

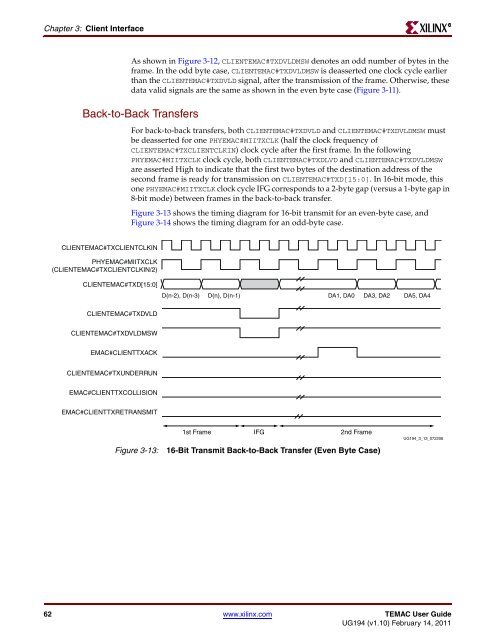

For back-to-back transfers, both CLIENTE<strong>MAC</strong>#TXDVLD and CLIENTE<strong>MAC</strong>#TXDVLDMSW must<br />

be deasserted for one PHYE<strong>MAC</strong>#MIITXCLK (half the clock frequency of<br />

CLIENTE<strong>MAC</strong>#TXCLIENTCLKIN) clock cycle after the first frame. In the following<br />

PHYE<strong>MAC</strong>#MIITXCLK clock cycle, both CLIENTE<strong>MAC</strong>#TXDLVD and CLIENTE<strong>MAC</strong>#TXDVLDMSW<br />

are asserted High to indicate that the first two bytes of the destination address of the<br />

second frame is ready for transmission on CLIENTE<strong>MAC</strong>#TXD[15:0]. In 16-bit mode, this<br />

one PHYE<strong>MAC</strong>#MIITXCLK clock cycle IFG corresponds to a 2-byte gap (versus a 1-byte gap in<br />

8-bit mode) between frames in the back-to-back transfer.<br />

Figure 3-13 shows the timing diagram for 16-bit transmit for an even-byte case, and<br />

Figure 3-14 shows the timing diagram for an odd-byte case.<br />

D(n-2), D(n-3) D(n), D(n-1) DA1, DA0 DA3, DA2 DA5, DA4<br />

1st Frame IFG 2nd Frame<br />

Figure 3-13: 16-Bit Transmit Back-to-Back Transfer (Even Byte Case)<br />

<strong>UG194</strong>_3_13_072206<br />

62 www.xilinx.com TE<strong>MAC</strong> User Guide<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

R