Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Chapter 6: Physical Interface<br />

Loopback itself can be enabled or disabled by writing to the PCS/PMA Sublayer Control<br />

Register (Register 0). The loopback position can be controlled through the Loopback<br />

Control Register (Register 17). See “1000BASE-X PCS/PMA Management Registers,” page<br />

122 for details. Alternatively, loopback can be controlled by setting the<br />

E<strong>MAC</strong>#_PHYLOOPBACKMSB and E<strong>MAC</strong>#_GTLOOPBACK attributes. See Chapter 2 for<br />

details.<br />

Serial Gigabit Media Independent Interface (SGMII)<br />

Generic<br />

Host Bus<br />

DCR Bus<br />

<strong>Ethernet</strong> <strong>MAC</strong> PCS/PMA Sublayer<br />

Flow Control<br />

Interface<br />

Host<br />

Interface<br />

DCR Bridge<br />

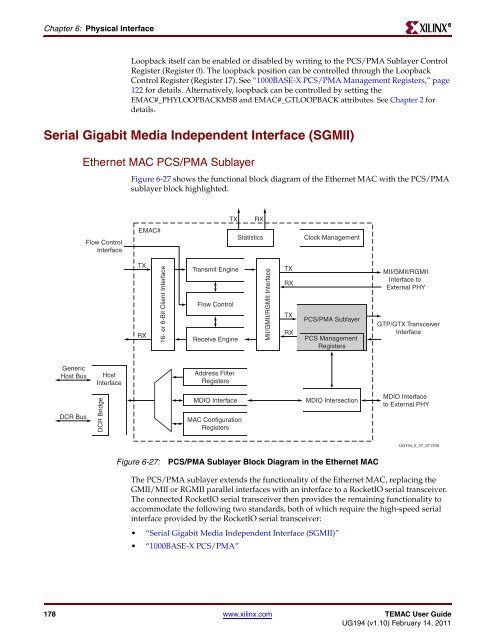

Figure 6-27 shows the functional block diagram of the <strong>Ethernet</strong> <strong>MAC</strong> with the PCS/PMA<br />

sublayer block highlighted.<br />

E<strong>MAC</strong>#<br />

TX<br />

RX<br />

16- or 8-Bit Client Interface<br />

Transmit Engine<br />

Flow Control<br />

Receive Engine<br />

Address Filter<br />

Registers<br />

MDIO Interface<br />

<strong>MAC</strong> Configuration<br />

Registers<br />

Figure 6-27: PCS/PMA Sublayer Block Diagram in the <strong>Ethernet</strong> <strong>MAC</strong><br />

The PCS/PMA sublayer extends the functionality of the <strong>Ethernet</strong> <strong>MAC</strong>, replacing the<br />

GMII/MII or RGMII parallel interfaces with an interface to a RocketIO serial transceiver.<br />

The connected RocketIO serial transceiver then provides the remaining functionality to<br />

accommodate the following two standards, both of which require the high-speed serial<br />

interface provided by the RocketIO serial transceiver:<br />

“Serial Gigabit Media Independent Interface (SGMII)”<br />

“1000BASE-X PCS/PMA”<br />

TX RX<br />

Statistics<br />

Clock Management<br />

MII/GMII/RGMII<br />

Interface to<br />

External PHY<br />

GTP/GTX Transceiver<br />

Interface<br />

MDIO Interface<br />

to External PHY<br />

<strong>UG194</strong>_6_27_071709<br />

178 www.xilinx.com TE<strong>MAC</strong> User Guide<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

MII/GMII/RGMII Interface<br />

TX<br />

RX<br />

TX<br />

RX<br />

PCS/PMA Sublayer<br />

PCS Management<br />

Registers<br />

MDIO Intersection<br />

R