Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Chapter 6: Physical Interface<br />

SGMII Auto-Negotiation<br />

<strong>Virtex</strong>-5 <strong>FPGA</strong><br />

<strong>Ethernet</strong><br />

<strong>MAC</strong><br />

Processor<br />

Overview of Operation<br />

Host Interface<br />

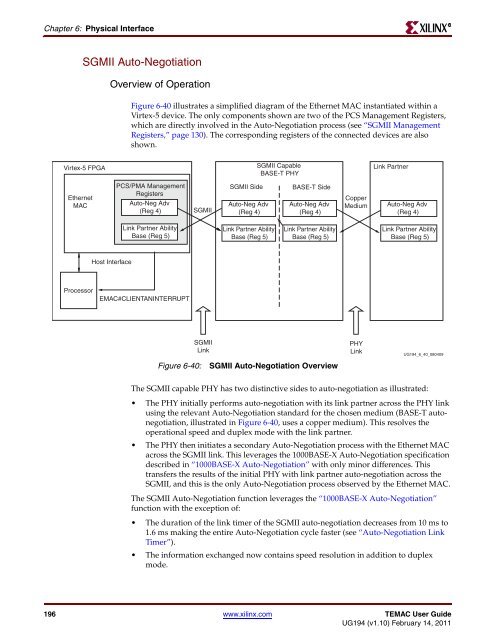

Figure 6-40 illustrates a simplified diagram of the <strong>Ethernet</strong> <strong>MAC</strong> instantiated within a<br />

<strong>Virtex</strong>-5 device. The only components shown are two of the PCS Management Registers,<br />

which are directly involved in the Auto-Negotiation process (see “SGMII Management<br />

Registers,” page 130). The corresponding registers of the connected devices are also<br />

shown.<br />

PCS/PMA Management<br />

Registers<br />

Auto-Neg Adv<br />

(Reg 4)<br />

Link Partner Ability<br />

Base (Reg 5)<br />

E<strong>MAC</strong>#CLIENTANINTERRUPT<br />

SGMII<br />

SGMII<br />

Link<br />

SGMII Capable<br />

BASE-T PHY<br />

SGMII Side BASE-T Side<br />

Auto-Neg Adv<br />

(Reg 4)<br />

Link Partner Ability<br />

Base (Reg 5)<br />

Auto-Neg Adv<br />

(Reg 4)<br />

Link Partner Ability<br />

Base (Reg 5)<br />

Figure 6-40: SGMII Auto-Negotiation Overview<br />

Copper<br />

Medium<br />

Link Partner<br />

Auto-Neg Adv<br />

(Reg 4)<br />

Link Partner Ability<br />

Base (Reg 5)<br />

PHY<br />

Link <strong>UG194</strong>_6_40_080409<br />

The SGMII capable PHY has two distinctive sides to auto-negotiation as illustrated:<br />

The PHY initially performs auto-negotiation with its link partner across the PHY link<br />

using the relevant Auto-Negotiation standard for the chosen medium (BASE-T autonegotiation,<br />

illustrated in Figure 6-40, uses a copper medium). This resolves the<br />

operational speed and duplex mode with the link partner.<br />

The PHY then initiates a secondary Auto-Negotiation process with the <strong>Ethernet</strong> <strong>MAC</strong><br />

across the SGMII link. This leverages the 1000BASE-X Auto-Negotiation specification<br />

described in “1000BASE-X Auto-Negotiation” with only minor differences. This<br />

transfers the results of the initial PHY with link partner auto-negotiation across the<br />

SGMII, and this is the only Auto-Negotiation process observed by the <strong>Ethernet</strong> <strong>MAC</strong>.<br />

The SGMII Auto-Negotiation function leverages the “1000BASE-X Auto-Negotiation”<br />

function with the exception of:<br />

The duration of the link timer of the SGMII auto-negotiation decreases from 10 ms to<br />

1.6 ms making the entire Auto-Negotiation cycle faster (see “Auto-Negotiation Link<br />

Timer”).<br />

The information exchanged now contains speed resolution in addition to duplex<br />

mode.<br />

196 www.xilinx.com TE<strong>MAC</strong> User Guide<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

R