Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

DCM<br />

CLKFB CLK0<br />

CLKIN CLKDV<br />

CLKDV_DIVIDE = 2.0<br />

R<br />

Tx<br />

and<br />

Rx<br />

Client<br />

Logic<br />

BUFG<br />

BUFG<br />

BUFG<br />

X<br />

<strong>Ethernet</strong> <strong>MAC</strong><br />

PHYE<strong>MAC</strong>#GTXCLK<br />

PHYE<strong>MAC</strong>#TXGMIIMIICLKIN<br />

E<strong>MAC</strong>#PHYTXGMIIMIICLKOUT<br />

CLIENTE<strong>MAC</strong>#TXCLIENTCLKIN<br />

E<strong>MAC</strong>#CLIENTTXCLIENTCLKOUT<br />

PHYE<strong>MAC</strong>#MIITXCLK<br />

CLIENTE<strong>MAC</strong>#RXCLIENTCLKIN<br />

E<strong>MAC</strong>#CLIENTRXCLIENTCLKOUT<br />

PHYE<strong>MAC</strong>#RXCLK<br />

CLIENTE<strong>MAC</strong>#DCMLOCKED<br />

Serial Gigabit Media Independent Interface (SGMII)<br />

125 MHz IBUFDS<br />

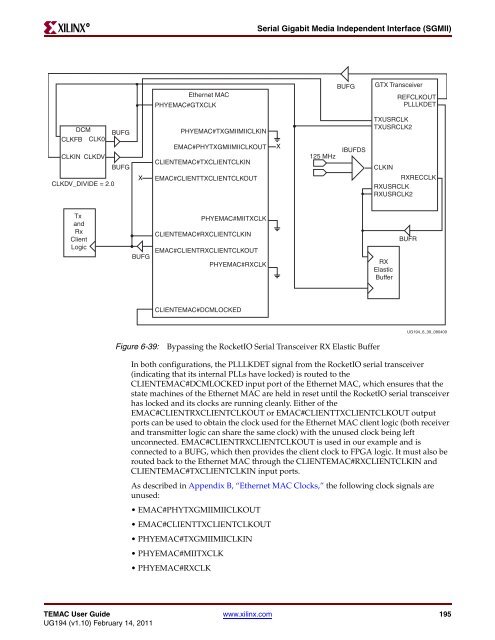

Figure 6-39: Bypassing the RocketIO Serial Transceiver RX Elastic Buffer<br />

GTX Transceiver<br />

TXUSRCLK<br />

TXUSRCLK2<br />

In both configurations, the PLLLKDET signal from the RocketIO serial transceiver<br />

(indicating that its internal PLLs have locked) is routed to the<br />

CLIENTE<strong>MAC</strong>#DCMLOCKED input port of the <strong>Ethernet</strong> <strong>MAC</strong>, which ensures that the<br />

state machines of the <strong>Ethernet</strong> <strong>MAC</strong> are held in reset until the RocketIO serial transceiver<br />

has locked and its clocks are running cleanly. Either of the<br />

E<strong>MAC</strong>#CLIENTRXCLIENTCLKOUT or E<strong>MAC</strong>#CLIENTTXCLIENTCLKOUT output<br />

ports can be used to obtain the clock used for the <strong>Ethernet</strong> <strong>MAC</strong> client logic (both receiver<br />

and transmitter logic can share the same clock) with the unused clock being left<br />

unconnected. E<strong>MAC</strong>#CLIENTRXCLIENTCLKOUT is used in our example and is<br />

connected to a BUFG, which then provides the client clock to <strong>FPGA</strong> logic. It must also be<br />

routed back to the <strong>Ethernet</strong> <strong>MAC</strong> through the CLIENTE<strong>MAC</strong>#RXCLIENTCLKIN and<br />

CLIENTE<strong>MAC</strong>#TXCLIENTCLKIN input ports.<br />

As described in Appendix B, “<strong>Ethernet</strong> <strong>MAC</strong> Clocks,” the following clock signals are<br />

unused:<br />

E<strong>MAC</strong>#PHYTXGMIIMIICLKOUT<br />

E<strong>MAC</strong>#CLIENTTXCLIENTCLKOUT<br />

PHYE<strong>MAC</strong>#TXGMIIMIICLKIN<br />

PHYE<strong>MAC</strong>#MIITXCLK<br />

PHYE<strong>MAC</strong>#RXCLK<br />

TE<strong>MAC</strong> User Guide www.xilinx.com 195<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

X<br />

BUFG<br />

CLKIN<br />

REFCLKOUT<br />

PLLLKDET<br />

RXRECCLK<br />

RXUSRCLK<br />

RXUSRCLK2<br />

RX<br />

Elastic<br />

Buffer<br />

BUFR<br />

<strong>UG194</strong>_6_39_080409