Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

TX CLIENT<br />

LOGIC<br />

RX CLIENT<br />

LOGIC<br />

R<br />

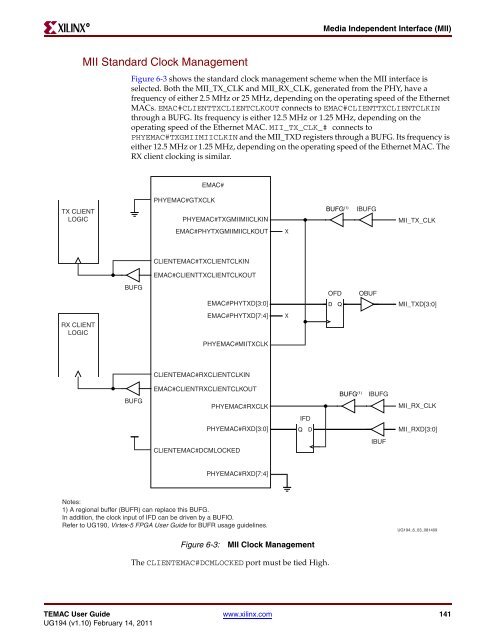

MII Standard Clock Management<br />

Media Independent Interface (MII)<br />

Figure 6-3 shows the standard clock management scheme when the MII interface is<br />

selected. Both the MII_TX_CLK and MII_RX_CLK, generated from the PHY, have a<br />

frequency of either 2.5 MHz or 25 MHz, depending on the operating speed of the <strong>Ethernet</strong><br />

<strong>MAC</strong>s. E<strong>MAC</strong>#CLIENTTXCLIENTCLKOUT connects to E<strong>MAC</strong>#CLIENTTXCLIENTCLKIN<br />

through a BUFG. Its frequency is either 12.5 MHz or 1.25 MHz, depending on the<br />

operating speed of the <strong>Ethernet</strong> <strong>MAC</strong>. MII_TX_CLK_# connects to<br />

PHYE<strong>MAC</strong>#TXGMIIMIICLKIN and the MII_TXD registers through a BUFG. Its frequency is<br />

either 12.5 MHz or 1.25 MHz, depending on the operating speed of the <strong>Ethernet</strong> <strong>MAC</strong>. The<br />

RX client clocking is similar.<br />

BUFG<br />

BUFG<br />

E<strong>MAC</strong>#<br />

PHYE<strong>MAC</strong>#GTXCLK<br />

PHYE<strong>MAC</strong>#TXGMIIMIICLKIN<br />

E<strong>MAC</strong>#PHYTXGMIIMIICLKOUT<br />

CLIENTE<strong>MAC</strong>#TXCLIENTCLKIN<br />

E<strong>MAC</strong>#CLIENTTXCLIENTCLKOUT<br />

E<strong>MAC</strong>#PHYTXD[3:0]<br />

E<strong>MAC</strong>#PHYTXD[7:4]<br />

PHYE<strong>MAC</strong>#MIITXCLK<br />

CLIENTE<strong>MAC</strong>#RXCLIENTCLKIN<br />

E<strong>MAC</strong>#CLIENTRXCLIENTCLKOUT<br />

PHYE<strong>MAC</strong>#RXCLK<br />

PHYE<strong>MAC</strong>#RXD[3:0]<br />

CLIENTE<strong>MAC</strong>#DCMLOCKED<br />

PHYE<strong>MAC</strong>#RXD[7:4]<br />

Notes:<br />

1) A regional buffer (BUFR) can replace this BUFG.<br />

In addition, the clock input of IFD can be driven by a BUFIO.<br />

Refer to UG190, <strong>Virtex</strong>-5 <strong>FPGA</strong> User Guide for BUFR usage guidelines.<br />

Figure 6-3: MII Clock Management<br />

The CLIENTE<strong>MAC</strong>#DCMLOCKED port must be tied High.<br />

<strong>UG194</strong>_6_03_081409<br />

TE<strong>MAC</strong> User Guide www.xilinx.com 141<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

X<br />

X<br />

IFD<br />

Q<br />

D<br />

BUFG (1)<br />

OFD<br />

D Q<br />

BUFG (1)<br />

IBUFG<br />

OBUF<br />

IBUFG<br />

IBUF<br />

MII_TX_CLK<br />

MII_TXD[3:0]<br />

MII_RX_CLK<br />

MII_RXD[3:0]