Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

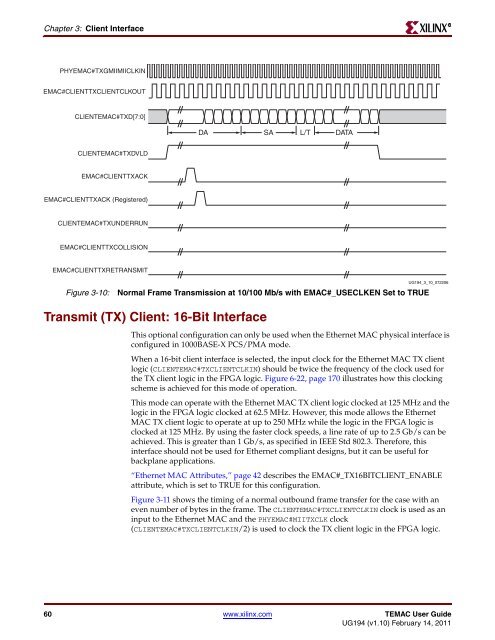

Chapter 3: Client Interface<br />

PHYE<strong>MAC</strong>#TXGMIIMIICLKIN<br />

E<strong>MAC</strong>#CLIENTTXCLIENTCLKOUT<br />

CLIENTE<strong>MAC</strong>#TXD[7:0]<br />

CLIENTE<strong>MAC</strong>#TXDVLD<br />

E<strong>MAC</strong>#CLIENTTXACK<br />

E<strong>MAC</strong>#CLIENTTXACK (Registered)<br />

CLIENTE<strong>MAC</strong>#TXUNDERRUN<br />

E<strong>MAC</strong>#CLIENTTXCOLLISION<br />

E<strong>MAC</strong>#CLIENTTXRETRANSMIT<br />

Figure 3-10: Normal Frame Transmission at 10/100 Mb/s with E<strong>MAC</strong>#_USECLKEN Set to TRUE<br />

Transmit (TX) Client: 16-Bit Interface<br />

DA SA L/T DATA<br />

<strong>UG194</strong>_3_10_072206<br />

This optional configuration can only be used when the <strong>Ethernet</strong> <strong>MAC</strong> physical interface is<br />

configured in 1000BASE-X PCS/PMA mode.<br />

When a 16-bit client interface is selected, the input clock for the <strong>Ethernet</strong> <strong>MAC</strong> TX client<br />

logic (CLIENTE<strong>MAC</strong>#TXCLIENTCLKIN) should be twice the frequency of the clock used for<br />

the TX client logic in the <strong>FPGA</strong> logic. Figure 6-22, page 170 illustrates how this clocking<br />

scheme is achieved for this mode of operation.<br />

This mode can operate with the <strong>Ethernet</strong> <strong>MAC</strong> TX client logic clocked at 125 MHz and the<br />

logic in the <strong>FPGA</strong> logic clocked at 62.5 MHz. However, this mode allows the <strong>Ethernet</strong><br />

<strong>MAC</strong> TX client logic to operate at up to 250 MHz while the logic in the <strong>FPGA</strong> logic is<br />

clocked at 125 MHz. By using the faster clock speeds, a line rate of up to 2.5 Gb/s can be<br />

achieved. This is greater than 1 Gb/s, as specified in IEEE Std 802.3. Therefore, this<br />

interface should not be used for <strong>Ethernet</strong> compliant designs, but it can be useful for<br />

backplane applications.<br />

“<strong>Ethernet</strong> <strong>MAC</strong> Attributes,” page 42 describes the E<strong>MAC</strong>#_TX16BITCLIENT_ENABLE<br />

attribute, which is set to TRUE for this configuration.<br />

Figure 3-11 shows the timing of a normal outbound frame transfer for the case with an<br />

even number of bytes in the frame. The CLIENTE<strong>MAC</strong>#TXCLIENTCLKIN clock is used as an<br />

input to the <strong>Ethernet</strong> <strong>MAC</strong> and the PHYE<strong>MAC</strong>#MIITXCLK clock<br />

(CLIENTE<strong>MAC</strong>#TXCLIENTCLKIN/2) is used to clock the TX client logic in the <strong>FPGA</strong> logic.<br />

60 www.xilinx.com TE<strong>MAC</strong> User Guide<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

R