Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

TX and<br />

RX<br />

Client<br />

Logic<br />

R<br />

SGMII Clock Management (LXT and SXT Devices)<br />

BUFG<br />

X<br />

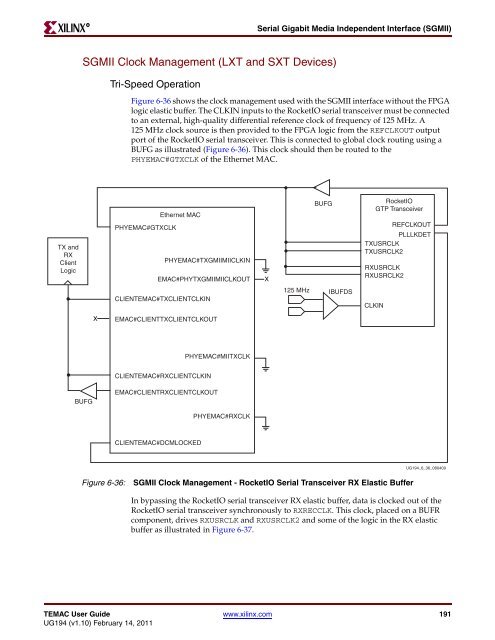

<strong>Tri</strong>-Speed Operation<br />

Serial Gigabit Media Independent Interface (SGMII)<br />

Figure 6-36 shows the clock management used with the SGMII interface without the <strong>FPGA</strong><br />

logic elastic buffer. The CLKIN inputs to the RocketIO serial transceiver must be connected<br />

to an external, high-quality differential reference clock of frequency of 125 MHz. A<br />

125 MHz clock source is then provided to the <strong>FPGA</strong> logic from the REFCLKOUT output<br />

port of the RocketIO serial transceiver. This is connected to global clock routing using a<br />

BUFG as illustrated (Figure 6-36). This clock should then be routed to the<br />

PHYE<strong>MAC</strong>#GTXCLK of the <strong>Ethernet</strong> <strong>MAC</strong>.<br />

PHYE<strong>MAC</strong>#GTXCLK<br />

<strong>Ethernet</strong> <strong>MAC</strong><br />

PHYE<strong>MAC</strong>#TXGMIIMIICLKIN<br />

E<strong>MAC</strong>#PHYTXGMIIMIICLKOUT<br />

CLIENTE<strong>MAC</strong>#TXCLIENTCLKIN<br />

E<strong>MAC</strong>#CLIENTTXCLIENTCLKOUT<br />

CLIENTE<strong>MAC</strong>#RXCLIENTCLKIN<br />

PHYE<strong>MAC</strong>#MIITXCLK<br />

E<strong>MAC</strong>#CLIENTRXCLIENTCLKOUT<br />

CLIENTE<strong>MAC</strong>#DCMLOCKED<br />

PHYE<strong>MAC</strong>#RXCLK<br />

125 MHz<br />

RocketIO<br />

GTP Transceiver<br />

PLLLKDET<br />

TXUSRCLK<br />

TXUSRCLK2<br />

RXUSRCLK<br />

RXUSRCLK2<br />

Figure 6-36: SGMII Clock Management - RocketIO Serial Transceiver RX Elastic Buffer<br />

In bypassing the RocketIO serial transceiver RX elastic buffer, data is clocked out of the<br />

RocketIO serial transceiver synchronously to RXRECCLK. This clock, placed on a BUFR<br />

component, drives RXUSRCLK and RXUSRCLK2 and some of the logic in the RX elastic<br />

buffer as illustrated in Figure 6-37.<br />

TE<strong>MAC</strong> User Guide www.xilinx.com 191<br />

<strong>UG194</strong> (v1.10) February 14, 2011<br />

X<br />

BUFG<br />

IBUFDS<br />

CLKIN<br />

REFCLKOUT<br />

<strong>UG194</strong>_6_36_080409