Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

Xilinx UG194 Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

R<br />

Interfacing to a Statistics Block<br />

Chapter 7<br />

To collect statistics information from an individual <strong>Ethernet</strong> <strong>MAC</strong>, a custom statistics<br />

counter can be implemented in the <strong>FPGA</strong> logic. A parameterizable <strong>Ethernet</strong> Statistics<br />

LogiCORE solution that fulfills all the requirements for statistics information collection<br />

is available through the CORE Generator tool (DS323, LogiCORE <strong>Ethernet</strong> Statistics Data<br />

Sheet, which provides a full description of the <strong>Ethernet</strong> Statistics LogiCORE block). Each<br />

<strong>Ethernet</strong> <strong>MAC</strong> that is used requires its own instance of this Statistics IP, as shown in<br />

Figure 2-1, page 27.<br />

This chapter describes how to connect the <strong>Ethernet</strong> <strong>MAC</strong> block to a Statistics block to allow<br />

the statistics registers of each <strong>Ethernet</strong> <strong>MAC</strong> to be accessed by either the host or DCR bus<br />

interface. A description of the address space that can be used for the statistics registers is<br />

provided to avoid register access contentions.<br />

“Statistics Vectors,” page 78 provides details on the statistics interface of the <strong>Ethernet</strong> <strong>MAC</strong><br />

and how the output signals encode the statistics vector information.<br />

Using the Host Bus to Access Statistics Registers<br />

When the <strong>Ethernet</strong> <strong>MAC</strong> is used with the host bus, interfacing to an <strong>FPGA</strong> logic-based<br />

statistics block is straight-forward. The statistics values can be read via a host interface that<br />

is shared between the statistics counters and the <strong>Ethernet</strong> <strong>MAC</strong> block.<br />

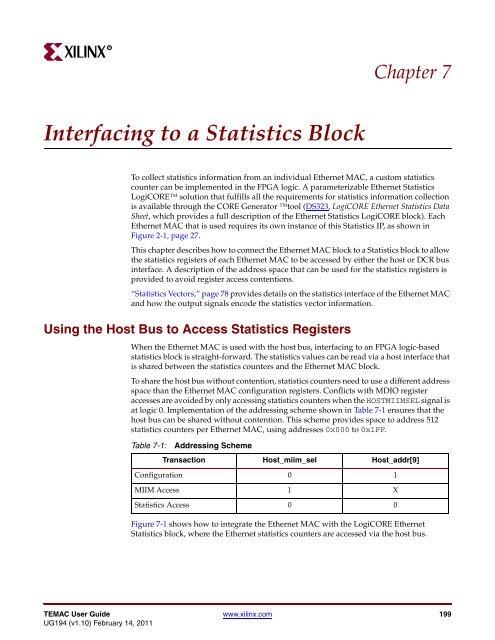

To share the host bus without contention, statistics counters need to use a different address<br />

space than the <strong>Ethernet</strong> <strong>MAC</strong> configuration registers. Conflicts with MDIO register<br />

accesses are avoided by only accessing statistics counters when the HOSTMIIMSEL signal is<br />

at logic 0. Implementation of the addressing scheme shown in Table 7-1 ensures that the<br />

host bus can be shared without contention. This scheme provides space to address 512<br />

statistics counters per <strong>Ethernet</strong> <strong>MAC</strong>, using addresses 0x000 to 0x1FF.<br />

Table 7-1: Addressing Scheme<br />

Transaction Host_miim_sel Host_addr[9]<br />

Configuration 0 1<br />

MIIM Access 1 X<br />

Statistics Access 0 0<br />

Figure 7-1 shows how to integrate the <strong>Ethernet</strong> <strong>MAC</strong> with the LogiCORE <strong>Ethernet</strong><br />

Statistics block, where the <strong>Ethernet</strong> statistics counters are accessed via the host bus.<br />

TE<strong>MAC</strong> User Guide www.xilinx.com 199<br />

<strong>UG194</strong> (v1.10) February 14, 2011